PCB and package designers need to be concerned with Signal Integrity (SI) issues to deliver electronic systems that work reliably in the field. EDA vendors like Siemens have helped engineers with SI analysis using a simulator called HyperLynx, dating all the way back to 1992. Siemens even wrote a 56-page e-book recently, Signal… Read More

Tag: impedance

WEBINARS: Board-Level EM Simulation Reduces Late Respin Drama

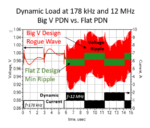

Advanced board designs are fertile ground for misbehavior in time and frequency domains. Relying on intuition, then waiting until near-final product for power integrity (PI) or EMI testing almost guarantees board respins are coming. Lumped-parameter simulations of on-board power delivery networks (PDNs) struggle with … Read More

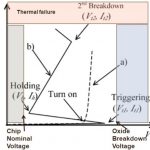

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More