We’re living in an era of good growth for semiconductor design companies, and it’s no secret that each new SoC that comes along contains hundreds of IP blocks, so IP design re-use is just an accepted way of getting to market more quickly with lower risks. But how do we really know that all of the new IP is really correct? … Read More

Tag: fractal technologies

Fractal CEO Update 2020

Rene Donkers, the company’s Co-founder and CEO, started his EDA career at Sagantec where he became responsible for world wide customer support and operations management. Ten years ago, Rene and a handful of people noticed a need in the design community for a standardized (portable) IP Validation approach to replace internal… Read More

Early IP Block Error Detection is Critical!

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

Webinar: IP Quality is a VERY Serious Problem

We just completed a run through of the upcoming IP & Library QA webinar that I am moderating with Fractal and let me tell you it is a must see for management level Semiconductor Design and Semiconductor IP companies as well as the Foundries. Seriously, if you are an IP company you had better be up on the latest QA checks if you want … Read More

CEO Interview: Rene Donkers of Fractal Technologies

Fractal is another one of those very successful emerging EDA companies that you don’t read a lot about, except on SemiWiki. Rene Donkers is co-founder and CEO of Fractal Technologies, a company addressing IP quality assurance. This is a niche in the SoC tooling market that deserves some justification. Why not use an IP as-is… Read More

Semiconductor IP QA Standards Get a Boost at #53DAC

At the #53DAC earlier this month held in Austin, Texas I met up with Renee Donkers, the founder of Fractal Technologies. His company has been focused on improving the quality of semiconductor IP cells through the use of automated checking software. The highest area of growth in EDA as measured by the ESD Alliance is in the reusable… Read More

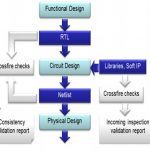

Crossfire on Continuous Path of Improvement

In an ever growing world of IPs, it’s essential that a tool which vouches to simplify designer’s job of IP development and help improving its quality remains versatile to encompass various formats, databases, common data models, standard libraries, scripting etc. that are used in the development of IPs and their exchange between… Read More

Standard Cell, IO and Hard IP Validation update

Every SoC team uses libraries of cells to get their new product to market quicker: Standard Cells, IO Cells and Hard IP blocks. One immediate question that comes to my mind is, “How clean are these cells?” Validating your cell libraries first makes sense, and will ensure that there are fewer surprises as your chip gets… Read More

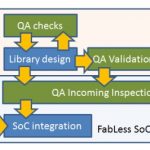

How About a Quality-Aware IP Design Flow

In the EDA world we use hyphens quite often to describe our technical approaches, like: DFM-aware, Power-aware, Variation-aware. I just read a white papertoday on the topic of Quality-Aware IP Design Flows, written by Fractal Technologies. If your group creates IP or re-uses IP, then there’s always the question about … Read More

Semiconductor IP Validation Gets Faster

Semiconductor IP continues to grow in use for SoC design, and many chips can now use hundreds of IP blocks from multiple vendors. Validating the quality of the IP blocks is an important step in the design process, and you could perform manual validation and inspection of each new IP block at the expense of time and engineering effort.… Read More