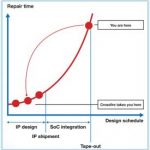

We’re living in an era of good growth for semiconductor design companies, and it’s no secret that each new SoC that comes along contains hundreds of IP blocks, so IP design re-use is just an accepted way of getting to market more quickly with lower risks. But how do we really know that all of the new IP is really correct? … Read More

Tag: crossfire

55DAC Trip Report IP Quality

This year I signed books in the Fractal booth (compliments of Fractal) and let me tell you it was quite an experience. IP quality is a very touchy subject and the source of many more tape-out delays than I had imagined. As it turns out, commercial IP is the biggest offender which makes no sense to me whatsoever. Even more shocking, one… Read More

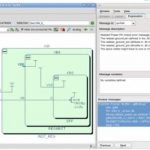

Cross View Static Validation

Improper handling of design validation could simply translate into a debugging exercise. In mainstream RTL2GDS flow, design implementation involves a top-level integration and lower-level block developments. These lower-level components, comprising of macros, IPs and standard cells are subjected to frequent abstraction… Read More

CEO Interview: Rene Donkers of Fractal Technologies

We (SemiWiki) have been working with Fractal for close to five years now publishing 25 blogs that have garnered more than 100,000 views. Generally speaking QA people are seen as the unsung heroes of EDA since the only time you really hear about them is when something goes wrong and a tapeout is delayed or a chip is respun.

FinFETs really… Read More

Good Library Hygiene Takes More Than an Occasional Scrub

You don’t shower only before you have to go to an important meeting (teenagers excepted). Surgical teams go further, demanding a strict regimen of hygiene be followed before anyone is allowed into an operating room. Yet we tend to assume that libraries and physical IP (analog, memories, other physical blocks) are checked and pronounced… Read More

Visual Quality

A few years ago, I started looking at data visualization methods as a way to make sense of large quantities of complex data. This is a technique that has become very popular in big data analytics where it is effectively impossible to see patterns in data in any other way. There are vast numbers of different types of diagram – treemap,… Read More

Power Checks for Your Libraries

When your design doesn’t work, who owns that problem? I don’t believe the answer to this question has changed significantly since semiconductor design started, despite distributed sourcing for IP and manufacturing. Some things like yield can (sometimes) be pushed back to the foundry, but mostly the design company owns the problem.… Read More

Quality in Hard IP

I was CTO at Atrenta, home of SpyGlass, for many years before the company was acquired by Synopsys, so I know a thing or two about IP quality, to paraphrase a popular commercial. The problem is that even in the best-run IP shops, errors happen. Sometimes they happen on simple changes, especially when you think “This IP has been very … Read More

Semiconductor IP QA Standards Get a Boost at #53DAC

At the #53DAC earlier this month held in Austin, Texas I met up with Renee Donkers, the founder of Fractal Technologies. His company has been focused on improving the quality of semiconductor IP cells through the use of automated checking software. The highest area of growth in EDA as measured by the ESD Alliance is in the reusable… Read More

DRC Concept for IP Qualification and SoC Integration

In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More