This informative webinar discusses a significant issue that is cropping up for sub-5nm designs. As the graphic above shows, modeling uncertainty at advanced nodes results in excessive guard banding. These guard bands result in reduced performance and profit. A loss of 25 – 35% in PPA is discussed, along with the lost profit associated… Read More

Tag: ClockEdge

WEBINAR: Reclaiming Clock Margin at 3nm and Below

At 3nm and below, clock networks have quietly become the dominant limiter of SoC power, performance, and yield. Yet most advanced-node designs still rely on abstraction-based signoff methodologies developed when voltage headroom was generous and interconnect effects were secondary.

That assumption no longer holds

As supply… Read More

What is the 3nm Pessimism Wall and Why is it An Economic Crisis?

Chip design is getting more difficult as technology advances. Everyone knows that. A lot of the discussion around these issues tends to focus on the demands posed by massive AI workloads and the challenges of shifting to heterogeneous multi-die design. While these create real problems, there is an underlying effect that is making… Read More

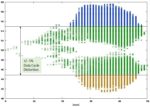

Taming Advanced Node Clock Network Challenges: Duty Cycle

As process nodes advance, circuit behavior becomes progressively more challenging to analyze and predict. Few systems reflect this challenge more clearly than the clock network. These large, complex networks no longer behave as ideal digital signals. Instead, they operate as distributed electrical systems shaped by non-linear… Read More

The Perils of Aging, From a Semiconductor Device Perspective

We‘re all aware of the challenges aging brings. I find the older I get, the more in touch I feel with those challenges. I still find it to be true that aging beats the alternative. I think most would agree. Human factors aside, I’d like to discuss the aging process as applied to the realm of semiconductor device physics. Here, as with… Read More

Afraid of mesh-based clock topologies? You should be

Digital logic chips synchronize all logic operations by using a clock signal connected to flip-flops or latches, and the clock is distributed across the entire chip. The ultimate goal is to have a clock signal that arrives at the exact same moment in time at all clocked elements. If the clock arrives too early or too late from the PLL… Read More

Clock Verification for Mobile SoCs

The relentless advancement of mobile phone technology continues to push boundaries, demanding SoCs that deliver ever-increasing performance while preserving extensive battery life. To meet these demands, the industry is progressively embracing lower technology nodes with current designs being taped-out at 5nm or below.… Read More

Methodology to Minimize the Impact of Duty Cycle Distortion in Clock Distribution Networks

Synchronous circuits dominate the electronic world because clocking eases the design of circuits compared to asynchronous circuits. At the same time, clocking also introduces its share of challenges to overcome. No wonder, a tremendous amount of time and effort have been spent over the years on developing and implementing … Read More

WEBINAR: Challenges in analyzing High Performance clocks at 7nm and below process nodes

Proper clock functionality and performance are essential for SoC operation. Static timing analysis (STA) tools have served well for verifying clocks, yet with new advanced process nodes, lower operating voltages, higher clock speeds and higher reliability requirements, STA tools alone can’t perform the kinds of analysis… Read More