You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

By Ujjwal Negi – Siemens EDA

Multi-die architectures are redefining the limits of chip performance and scalability through the integration of multiple dies into a single package to deliver unprecedented computing power, flexibility, and efficiency. At the heart of this transformation is the Universal Chiplet Interconnect… Read More

Ever wonder why coherent networks are needed beyond server design? The value of cache coherence in a multi-core or many-core server is now well understood. Software developers want to write multi-threaded programs for such systems and expect well-defined behavior when accessing common memory locations. They reasonably expect… Read More

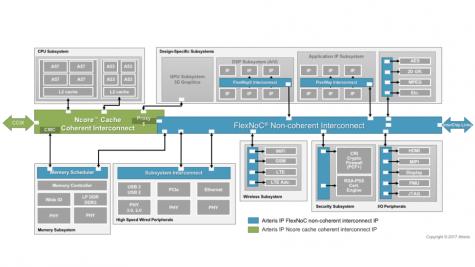

If a CPU or CPU cluster in an SoC is the brain of an SoC, then the interconnect is the rest of the central nervous system, connecting all the other processing and IO functions to that brain. This interconnect must enable these functions to communicate with the brain, with multiple types of memory, and with each other as quickly and predictably… Read More