IDC has forecasted that over the next five years, the Global Datasphere — the amount of data that’s created, transferred over the network and stored each year — will increase by over 3X to 175 zettabytes (Figure 1). Much of this is driven by the Internet of Things (IoT), video applications (including video streaming,… Read More

Tag: ccix

Verifying PCIe 5.0 with PLDA, Avery and Aldec

Mike Gianfagna, a fellow SemiWiki blogger and a one-time colleague at Atrenta shared a useful piece of marketing advice. If your company is not the biggest fish in the pond and you want to appear more significant, team up with other companies to put on an event, say a webinar. Pick your partners so that you can jointly offer a larger,… Read More

Machine Learning Drives Transformation of Semiconductor Design

Machine learning is transforming how information processing works and what it can accomplish. The push to design hardware and networks to support machine learning applications is affecting every aspect of the semiconductor industry. In a video recently published by Synopsys, Navraj Nandra, Sr. Director of Marketing, takes… Read More

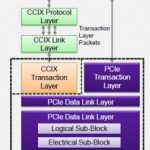

CCIX Protocol Push PCI Express 4.0 up to 25G

The CCIX consortium has developed the Cache Coherent Interconnect for Accelerators (X) protocol. The goal is to support cache coherency, allowing faster and more efficient sharing of memory between processors and accelerators, while utilizing PCIe 4.0 as transport layer. With Ethernet, PCI Express is certainly the most popular… Read More