At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Tag: bus

Enterprise SSD SOC’s Call for a Different Interconnect Approach

The move to SSD storage for enterprise use brings with it the need for difficult to design enterprise capable SSD controller SOC’s. The benefits of SSD in hyperscale data centers are clear. SSD’s offer higher reliability due to the elimination of moving parts. They have a smaller foot print, use less power and offer much better performance.… Read More

Xilinx picks another winner…

Just as important as block RAMs, IO and DSP48’s is what interconnect or fabric is going to be used when considering SoC FPGA designs. I think Xilinx has found the winning combination. What is paramount to the new SoC FPGA methodologies is not only the challenge of moving huge amounts of data around; we are now to consider data… Read More

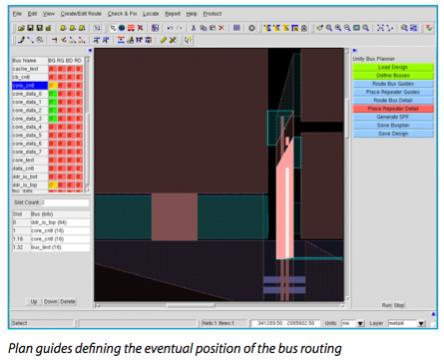

Driving in the bus lane

Modern microprocessor and memory designs often have hundreds of datapaths that traverse the width of the chip, many of them very wide (over one thousand signals). To meet signal timing and slope targets for these buses, designers must insert repeater cells to improve the speed of the signal. Until now, the operations associated… Read More