You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

How do you get a shortage while not growing???

Intel Announced earnings in January. Then David Zinsner presented updates on business this week. David is open when talking and always shares 2-3 things he probably should not share. Often he shares things some of us know, but we cannot present because it is not public. Then he makes it… Read More

In the rapidly evolving landscape of semiconductor technology, the Universal Chiplet Interconnect Express (UCIe) emerges as a groundbreaking open standard designed to revolutionize on-package chiplet integrations. Presented by Dr. Debendra Das Sharma, Chair of the UCIe Consortium and Intel Senior Fellow, at the Chiplet… Read More

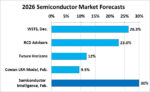

The global semiconductor market in 2025 was $792 billion, according to WSTS. 2025 was up 25.6% from 2024, the strongest growth since 26.2% in the COVID recovery year 2021. The increase was driven by AI, with Nvidia revenues up 65%. The major memory companies (Samsung, SK Hynix, Micron Technology, Kioxia and Sandisk) all cited AI… Read More

Synopsys and AMD were recently selected by the World Economic Forum for inclusion in the WEF’s MINDS (Meaningful, Intelligent, Novel, Deployable Solutions) AI program, recognizing their leadership and real-world impact in applying generative and agentic AI to semiconductor design and engineering. This distinction places… Read More

The world semiconductor market was $208 billion in third-quarter 2025, according to WSTS. This marks the first time the market has been above $200 billion. 3Q 2025 was up 15.8% from 2Q 2025, the highest quarter-to-quarter growth since 19.9% in 2Q 2009. 3Q 2025 was up 25.1% from 3Q 2024, the highest growth versus a year earlier since… Read More

ARM’s Quiet Coup in DPUs

The datacenter is usually framed as a contest between CPUs (x86, ARM, RISC-V) and GPUs (NVIDIA, AMD, custom ASICs). But beneath those high-profile battles, another silent revolution has played out: ARM quietly displaced Intel and AMD in the Data Processing Unit (DPU) market.

DPUs — also called SmartNICs… Read More

There is a lot of talk about where Intel went wrong, the latest is missing AI, but people seem to forget one of the more defining blunders in the history of Intel. In April of 2012 Kirk Skaugen, the new general manager of Intel’s client PC group, moderated a Q&A with Mark Bohr, a 33+ year Intel fellow, and Brad Heaney, the Ivy Bridge… Read More

Modern EVs are prime examples of software-defined systems, so I attended a #62DAC panel session hosted by Siemens to learn more from experts at Collins Aerospace, Arm, AMD and Siemens. Here’s the list of panelists that span several domains, and what follows is my paraphrase of the discussion topics.

Panel Discussion

Q: How does… Read More

In a keynote by Michaela Blott, AMD Senior Fellow, at the 62nd Design Automation Conference (DAC) on July 8, 2025, explored the trends shaping the AI revolution, emphasizing inference efficiency and hardware customization. While acknowledging AMD’s efforts in scaling GPUs and achieving energy efficiency goals (30x… Read More

President Donald Trump has initially excluded semiconductors from his latest round of U.S. tariffs. However, he could put tariffs on semiconductors in the future. If tariffs are placed on semiconductors imported to the U.S., how would that affect U.S.-based semiconductor companies? The chart below shows U.S. semiconductor… Read More