One of the most unique acronyms that I learned about this past year is ACAP from Xilinx, which stands for Adaptive Compute Acceleration Platform. At the recent Cadence LIVE event, I had the pleasure of watching Pei Yao, a Xilinx senior staff CAD engineer, as she talked about the challenges of getting all the analog and mixed-signals… Read More

Tag: ACAP

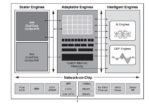

Xilinx Moves from Internal Flow to Commercial Flow for IP Integration

I’ll never forget first learning about Xilinx when they got started back in 1984, because the concept of a Field Programmable Gate Array (FPGA) was so simple and elegant, it was rows and columns of logic gates that a designer could program to perform any logic function, then connect that logic to IO pads to drive other chips … Read More