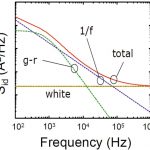

Electronics noise is often described as “white,” spread evenly across a band, typical on older semiconductor processes where thermal and shot noise dominate. As transistors shrink, “pink” 1/f noise takes over at low frequencies – becoming stronger in advanced processes and quantum computing technology. But it’s not an easy… Read More

Tag: 1/f noise

Why is Low Frequency Noise Measurement for ICs Such a Big Deal?

Even digital designers need to be aware of how noise impacts their circuits because most clocked designs today use a Phase Locked Loop (PLL) block which contains a circuit called a Voltage Controlled Oscillator (VCO) that is quite sensitive in operation to the effects of noise and process variation. As process node scaling continues… Read More

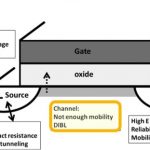

Low Frequency Noise Challenges IC Designs

AMS and RF IC designers have known for years that their circuits are sensitive to noise, because if you amplify noise on an input source to an amplifier circuit then your chip can start to produce wrong answers. Even digital SoC designers need to start taking notice because every SoC is filled with SRAM IP blocks, and at each shrinking… Read More