TSMC Roadmap 2022

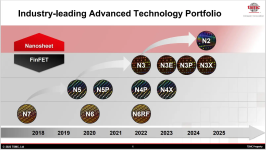

TSMC showcased its industry-leading advanced logic, specialty, and TSMC 3DFabric™ silicon stacking and advanced packaging technologies at its 29th Technology Symposium. Headlining this year’s events were TSMC’s innovative nanosheet-based 2nm technology, its most comprehensive 3nm technology portfolio to meet customers’ diverse product demands, and its industry-first N3AE solution that gives customers a head start on automotive product design to shorten product time-to-market. Hosting in-person and virtual events in parallel this year, TSMC attracted record attendance of more than 8,000 visitors in North America, Taiwan, Europe, China, and Japan, indicating continued strong customer interest in the Company.

Our customers never stop finding new ways to harness the power of silicon to create innovations that shall amaze the world for a better future. In the same spirit, TSMC never stands still, and we keep enhancing and advancing our process technologies with more performance, power efficiency, and functionality so their pipeline for innovation can continue flowing for many years to come.

- Dr. C.C. Wei, CEO of TSMC

Major Technology Highlights at the 2023 Technology Symposium Include

Customer trust and long-term partnerships are the bedrock to TSMC’s success. This year, TSMC also invited heavyweight customers from around the globe to share collaborative breakthroughs in artificial intelligence (AI), 5G communication, high-performance computing (HPC), and automotive applications. In addition, this year’s Innovation Zone featured 48 emerging startup customers who shared their world-changing innovative technologies and products. These covered high-profile applications such as power-efficient AI chipsets, automotive controllers, gallium nitride (GaN) power modules, energy-harvesting controllers, and medical sensors. The attendee-voted Demo of the Year Award entered its second year this year and had expanded from North America to include Europe. Ambiq was voted the North America award winner for its real-time heart-monitoring solutions driven by edge AI and ultra-low power technologies, while Cambridge GaN Devices was most popular in Europe for its high-performing, energy-saving GaN power modules for consumer electronics, data center power supplies, and electric vehicle (EV) on-board chargers.

Customers Around the Globe Share Their Insights and Successful Stories of Collaborating with TSMC

Semiconductors have become critical to drive the 21st century economic growth and human progress. HPC, mobile, automotive, and Internet of Things (IoT) applications continue to fuel chip demand and growth, which is a testament to how the world runs on semiconductors. TSMC will continue to invest in its technology advancements, enhance its 3D IC capabilities, and expand its capacity and global manufacturing footprint to meet global customer demands, to help unleash customer innovations, and to achieve a better, safer, and greener future together.