As expected, security was a big topic at DAC this year. The growth of AI has demanded complex, purpose-built semiconductors to run ever-increasing workloads. AI has helped to design those complex chips more efficiently and with less power demands. There was a lot of discussion on these topics. But there is another part of this trend. While sophisticated, generative AI makes it easier to design complex AI chips, it also makes it easier to attack and compromise those same chips. GenAI must also be used to harden designs from these attacks to keep innovation moving ahead.

Caspia is a company that clearly sees this challenge and has developed a comprehensive approach to reduce these risks. At DAC, Caspia co-founders hosted a workshop on Sunday, the company presented a SKYTalk on Tuesday and issued a press release detailing collaboration to add its security technology to Siemens Questa One. Let’s take a closer look at how Caspia focuses security requirements at DAC.

The Workshop

Sunday at DAC is when various workshops and tutorials are held. One of these events was the third AI/CAD for Hardware Security Workshop, or AICAD4Sec 2025. Building on the success of the first two events, this one aimed to embrace the transformative intersection of AI, CAD, and hardware security. The stated vision of AICAD4Sec is to establish a cutting-edge platform that shows advancements and sets the roadmap for secure, AI-enabled hardware design. Organizations that are involved include Google, Microsoft, Synopsys, and ARM, alongside academia and government agencies such as DARPA and AFRL.

The event was hosted by a small group of researchers, including two co-founders of Caspia Technologies.

Dr. Mark Tehranipoor, Department Chair & Intel Charles E. Young Chair in Cybersecurity at University of Florida ECE. He is a founding Director of the Florida Institute for Cybersecurity Research and a former Associate Chair and Program Director at the University of Florida. He has authored 16 books and over 230 invited talks and holds 22 patents. Mark is a recipient of the IEEE, ACM, and National Academy of Inventors fellowships.

Dr. Mark Tehranipoor, Department Chair & Intel Charles E. Young Chair in Cybersecurity at University of Florida ECE. He is a founding Director of the Florida Institute for Cybersecurity Research and a former Associate Chair and Program Director at the University of Florida. He has authored 16 books and over 230 invited talks and holds 22 patents. Mark is a recipient of the IEEE, ACM, and National Academy of Inventors fellowships.

Dr. Farimah Farahmandi, Wally Rhines Endowed Professor in Hardware Security and Assistant Professor at the University of Florida ECE. She is the Founding Director of the Silicon Design and Assurance Laboratory and is Associate Director of the Florida Institute of Cybersecurity and Edaptive Computing Transition Center. She has authored seven textbooks, 120+ journal/conference papers, and holds 12 patents issued/pending.

These are the folks who founded this workshop three years ago. The event on Sunday covered a wide range of topics, including:

- CAD Tools for Side-Channel Vulnerability Assessment (Power, Timing, and Electromagnetic Leakage)

- Security-Oriented Equivalency Checking and Property Validation

- Fault Injection Analysis and Countermeasure Integration in CAD

- CAD for Secure Packaging and Heterogeneous Integration

- Assessment of Physical Probing and Reverse Engineering Risks

- AI-Powered Tools for Pre-Silicon Vulnerability Mitigation and Countermeasure Suggestions

- Large Language Models for Security-Aware Design Automation

- ML-Enhanced Threat Detection Across Design Abstractions

- AI-Augmented Detection of Malicious Functionality in Hardware Designs

- AI-Enabled Security Verification for Emerging SoC Architectures

This workshop provided a great opportunity for researchers from many organizations to come together to develop a big picture plan. One attendee was quoted as saying, “I was very energized by the workshop today. It was a great dialogue, and I enjoyed the time with the Mark, Farimah, and the rest of the Caspia team.”

The SKYTalk

SKYTalks are keynote-style presentations delivered in the DAC Pavillion located on the show floor. Mark Tehranipoor delivered a very well received presentation entitled New Innovation Frontier with Large Language Models for SoC Security.

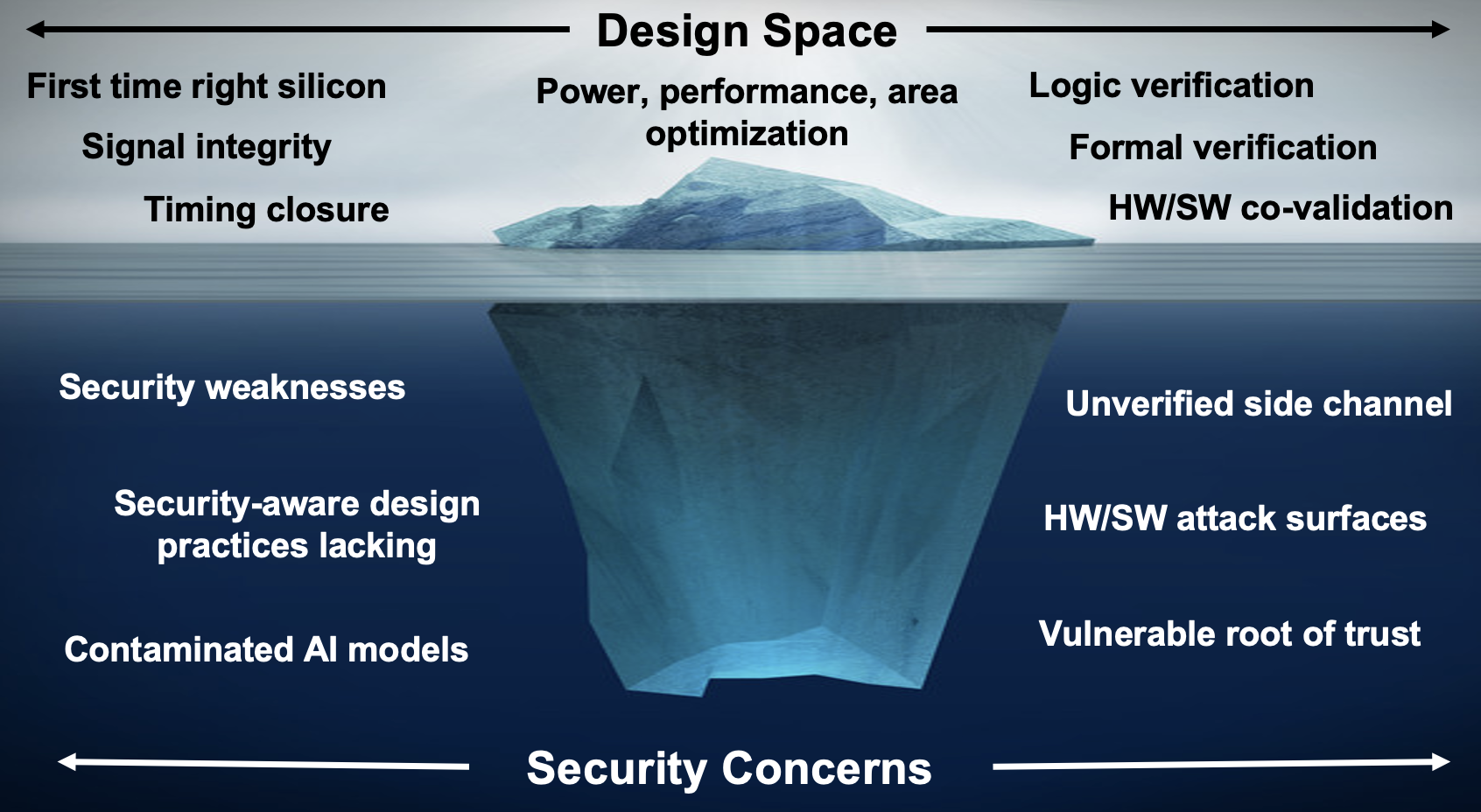

There were two parts to his talk. In the first part, he described the problem faced by design teams today. While there is a strong focus on performance, power and functional verification, there exists a significant blind spot regarding security verification. The graphic at the top of this post was used by Mark to illustrate the perils that lurk below the water line.

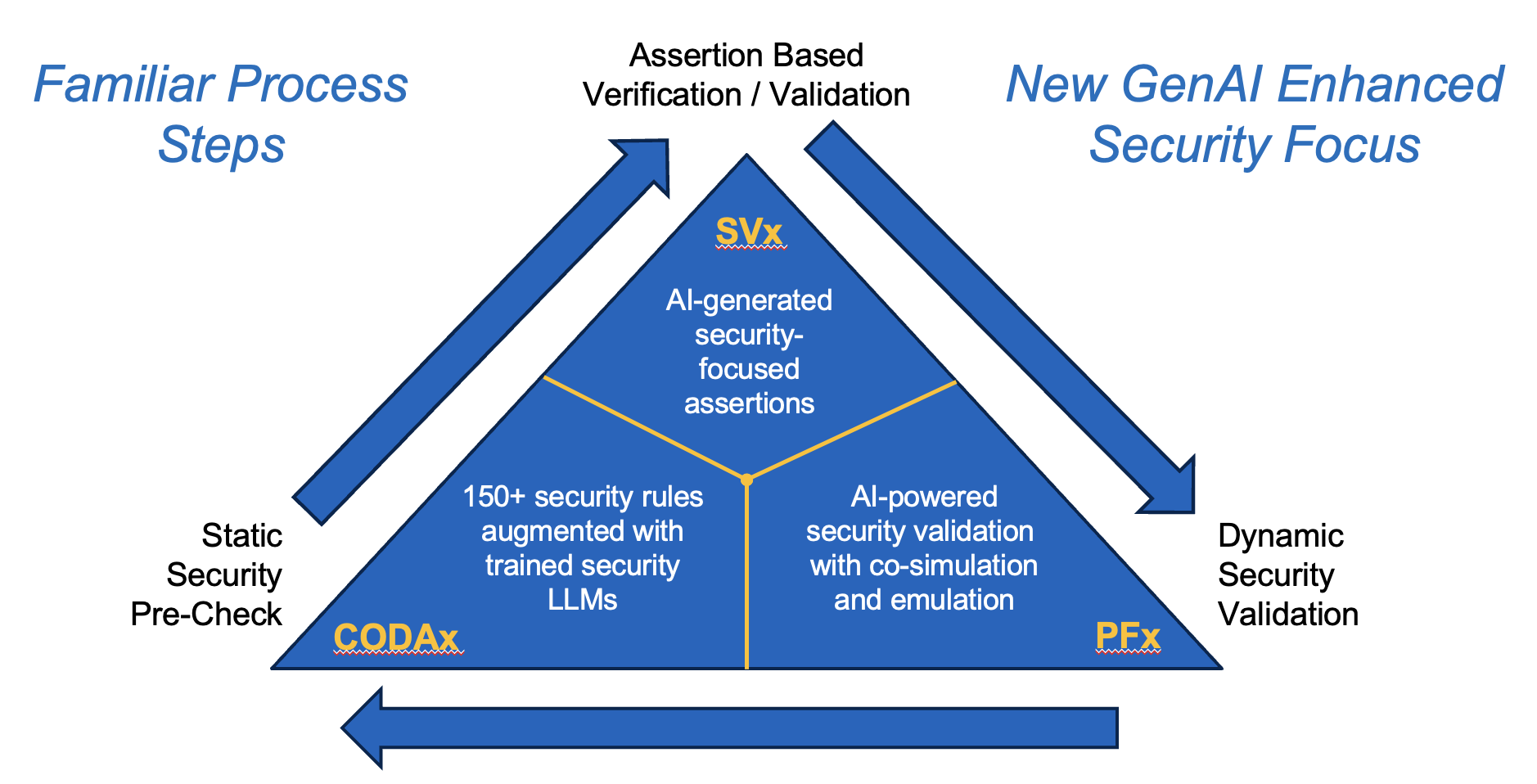

He cited several examples from recent headlines that show how significant and real these security threats are becoming. He described the platform Caspia is developing to address these security risks using GenAI technology. The LLM-powered security agents in this platform continually learn from real world behaviors so designers can stay ahead of new and emerging threats. The tools are designed to complement and not replace existing flows. These tools essentially adding GenAI fueled expert-level security verification to existing design flows. The figure below summarizes the current capabilities of the Caspia security verification platform.

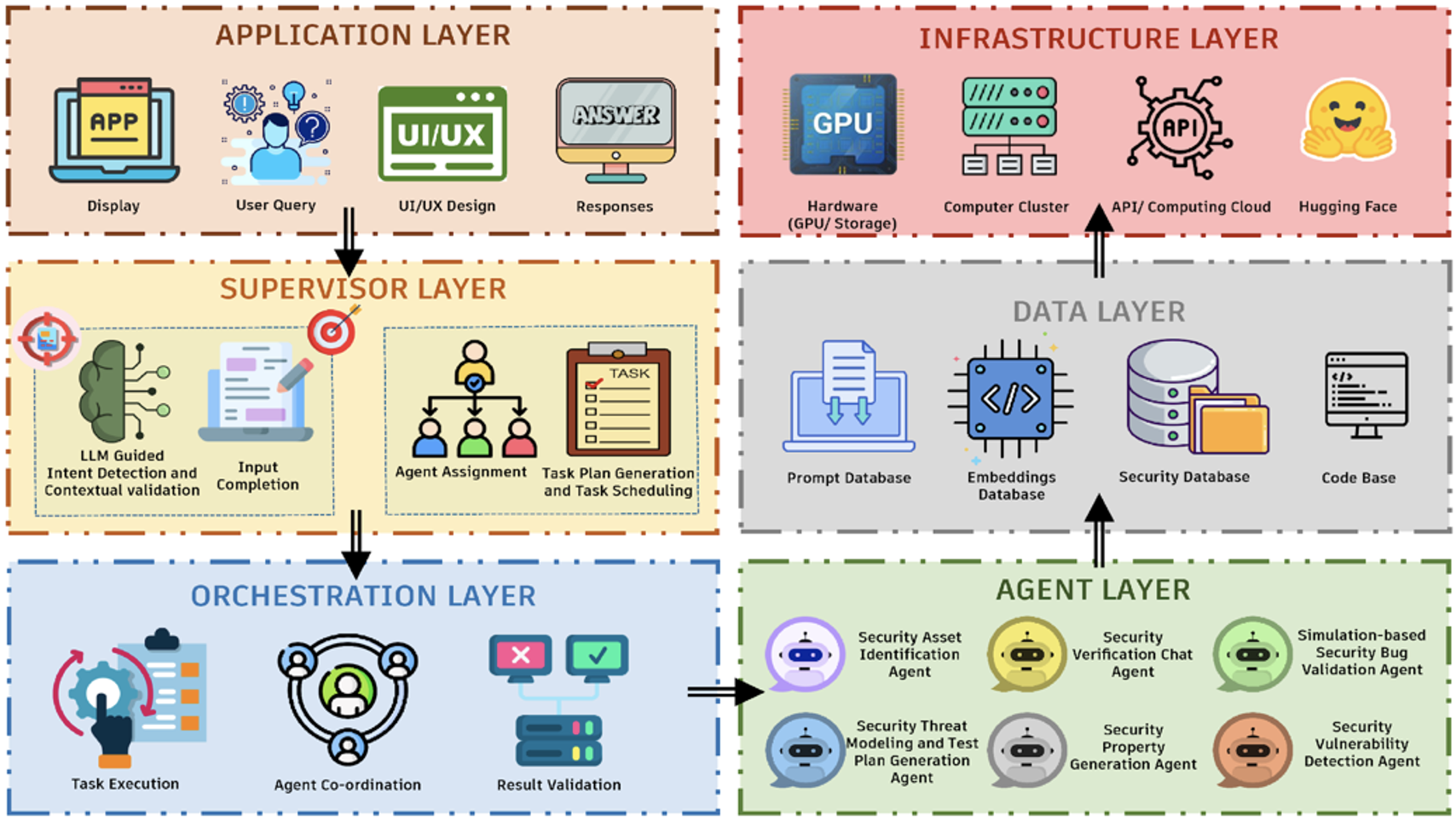

In the second part of his talk, Mark described the details of how GenAI can be applied to SoC security verification with real examples. He began by describing the overall architecture of the GenAI security platform. The layers of this platform and how they interact are summarized in the diagram below.

The functions of each layer can be summarized as follows:

Application Layer

- Handles user display, query submission, and UI/UX rendering

- Provides chat-based interface and structured responses for ease of interaction

Supervisor and Orchestrator Layers

- Performs LLM-driven user intent detection and input completion

- Assigns tasks to appropriate agent

- Generates and schedules task plans for execution

- Initiates and confirms execution of the tasks

Agent Layer

- Verification chat agent

- Security asset identification

- Threat modeling and test plan

- Security property generation

- Vulnerability detection

- Bug validation

Data Layer

- Stores and provides access to datasets of text embeddings

Infrastructure Layer

- Leverages cloud GPU clusters, APIs

- Ensures scalable deployment of LLM & secure backend

This system provides a robust environment to facilitate analysis of the design and interaction with the designer using highly focused security data to drive the overall process. Access to specialized security data is a key element to make the system useful for its intended purpose. Mark provided examples of results using general purpose LLMs (e.g., ChatGPT) and the specialized security LLMs and agents in this platform. The results from Caspia’s specialized technology were substantially more targeted, accurate and effective.

The Agent Layer is where specific analysis of a design occurs. Mark provided several examples of how security assets can be identified, analyzed for weaknesses and enhanced to deliver a security hardened design. This architecture will continue to grow and become more specialized and sophisticated over time.

The Press Release

Just before DAC began, Caspia issued a press release describing how Caspia and Siemens are collaborating to add Caspia’s portfolio of security technologies to expand security verification features in Siemens’ recently announced Questa™ One smart verification software portfolio. The Caspia platform is designed to add expert security verification to existing flows, so this announcement is an example of that strategy.

At DAC, there was a follow-on event at the Siemens booth related to this announcement. Siemens had a sound-proof, glass enclosed recording booth at the show where they recorded discussions with various companies about collaborative efforts. Mark Tehranipoor was interviewed in the Siemens recording booth about the work Caspia is doing with Siemens Digital Industries Software.

Mark covered the challenges design teams are facing and the technology Caspia is developing to address those challenges. The collaboration work is still in the early phase, so there will be more on this work going forward. The final slide in Mark’s presentation brought together several points of view on the work to illustrate the possibilities as shown below.

To Learn More

Security verification is a new and growing area for chip designers. I expect a lot more discussion on this topic at next year’s DAC, and Caspia appears to be positioned to lead the discussion. You can read the entire press release announcing the collaboration with Siemens here. There is an excellent interview with Caspia’s CEO, Rich Hegberg on SemiWiki here. And you can learn more about Capsia’s products and plans on the company’s website here. The interview in the Siemens booth will be added to the Caspia website, so check back to see this discussion. And that’s how Caspia focuses security requirements at DAC.

Also Read:

Caspia Technologies at the 2025 Design Automation Conference #62DAC

CEO Interview with Richard Hegberg of Caspia Technologies

Podcast EP245: A Conversation with Dr. Wally Rhines about Hardware Security and Caspia Technologies

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.