One of the goals of the recent RISC-V Summit was to demonstrate that the RISC-V movement is real – major programs by large organizations committing to development around the RISC-V ISA. I would say this goal was achieved. Many high-profile announcements and aggressive, new architectures based on RISC-V were presented. On day one, compelling keynotes from companies such as Ventana Micro Systems, Meta, Microchip, Qualcomm and Synopsys were on the agenda. But what about the smaller companies? At the end of day one, a group of these companies got a chance to tell conference attendees about the great work they were doing. Read on to get a feeling for the magnitude of the of the RISC-V movement as the Launchpad Showcase highlights smaller company innovation.

Three Minutes of Fame

The famous quote, “In the future, everyone will be world-famous for 15 minutes” has been attributed to Andy Warhol from the 1960’s. Who actually said it first is the subject of some debate. Regardless, the concept is quite relevant today thanks to ubiquitous social media platforms. At the end of the first day of the RISC-V Summit, Tiffany Sparks, director of marketing at RISC-V International kicked of a session that aimed to highlight a broad range of innovations being shown at the conference. Eight companies were chosen, and the 15 minutes of fame was reduced to three minutes to manage session length. Can eight individuals deliver a compelling and memorable message to a large audience at the end of a long day of presentations? Let’s find out…

Andes D25F-SE: The Superhero of RISC-V CPUs

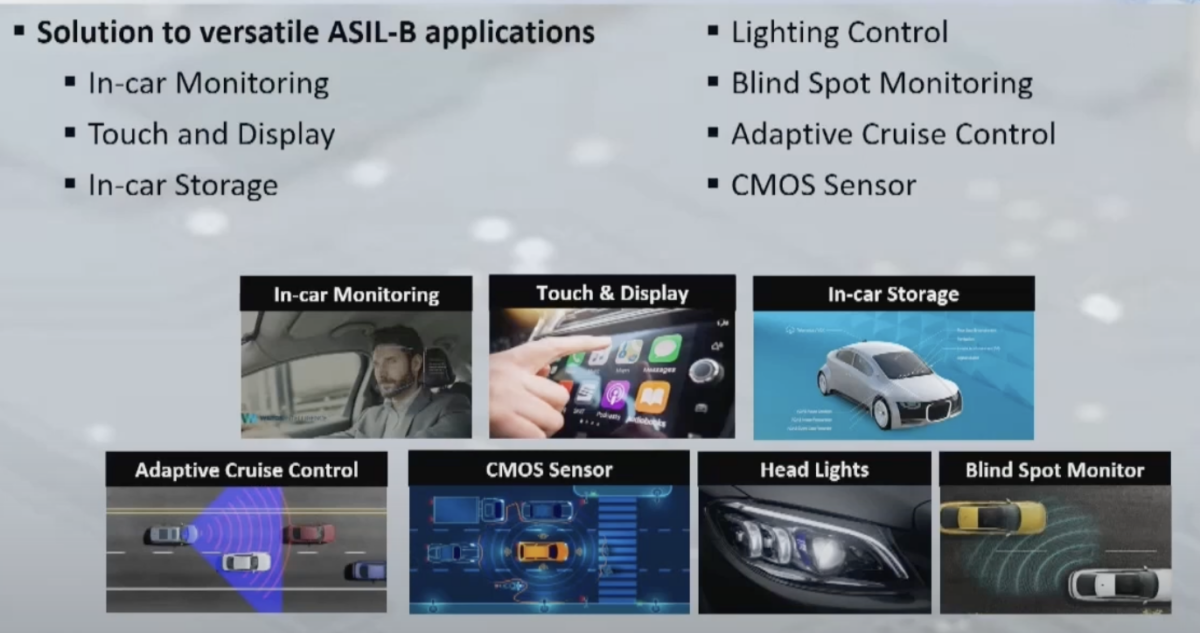

Marvin Chao, director of solution architect presented for Andes Technology. Marvin explained that the D25F-SE core is fully ASIL-B compliant and contains several extensions, making it useful in many automotive applications, as shown in the figure below.

The core has a five-stage, in-order single-issue architecture. Based on the AndesStar V5 32-bit architecture, it has the RV32 GCBP ISA with Andes extensions. The memory subsystem supports instructions and data caches up to 32KB each and instruction and data local memories up to 16MB each. The part has AXI or AHB ports and a local memory direct access port. For functional safety, there is support for things like core trap status bus interface, ECC protection, StackSafe, and PMP. The part will be ASIL-B certified in Q4, 2023.

Marvin explained that speed-ups in the range of 3X or more can be achieved. The performance and flexibility of this design does put it in the superhero category I believe.

Beagleboard.org: Technology Access Without Barriers

Jason Kridner, co-founder of beagleboard.org, presented a couple of new products from this non-profit organization. Its mission is to provide education in and collaboration around the design and use of open-source software and hardware in embedded computing. Jason presented two new boards.

The BeagleV-Ahead is aimed at high-performance mobile and edge applications. It contains a quad core C910 2GHZ with optimized video, graphics, neural, and audio processors. It supports out of order execution and supports H.264 and H.265. Jason went on to describe many more capabilities of the product, making it applicable in a wide range of applications. The best part is that it’s available for $149 in quantity, worldwide.

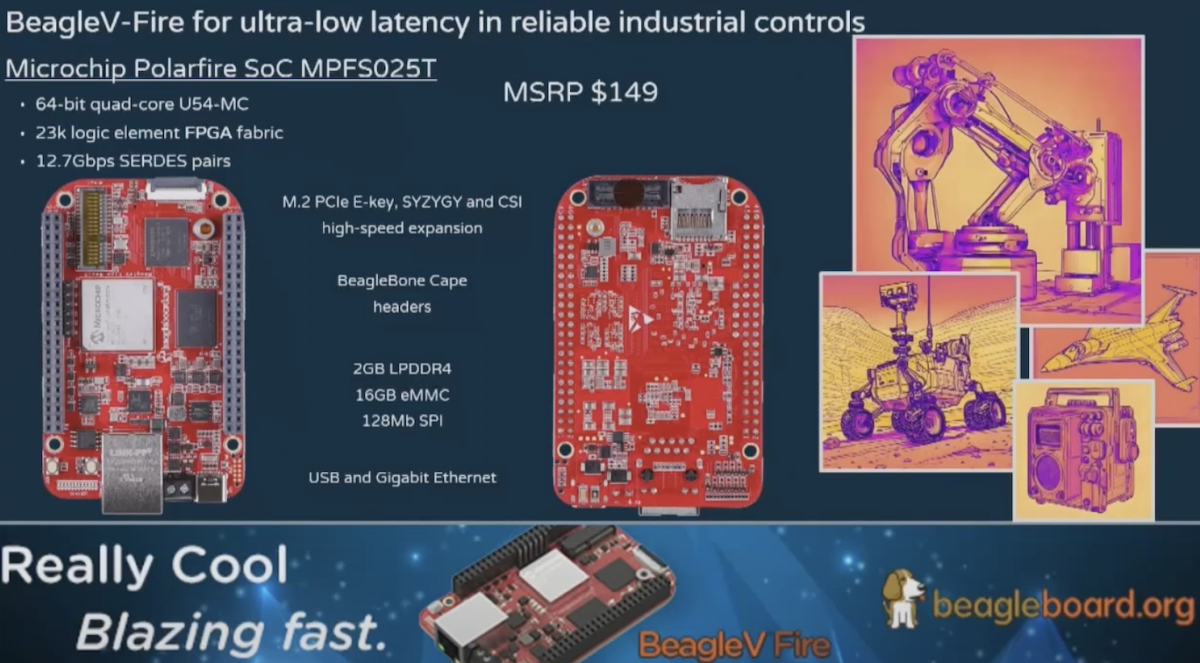

He also presented a product that was just announced, the BeagleV-Fire. This part uses a Microchip PolarFire SoC with an FPGA fabric, making experimentation easy. This one covers a lot of application space as well and is also available for $149. Below is more detail on it.

Jason ended his presentation with an offer to set up a meeting with him via the beagleboard.org website. He is there to help the community succeed, so he is personally committed to the mission of technology access without barriers.

Codasip: Meet Mr. Custom Compute

Mike Eftimakis is the VP of strategy and ecosystem at Codasip. He’s known around the company for his passion regarding custom compute. Mike pointed out that custom compute is the differentiator for Codasip, so his passion aligns well with company goals. He explained that Codasip decided from the beginning to take a different approach that would allow the flexibility needed to make custom compute a reality.

Mike explained that efficiency improvements of 1,000 – 10,000 percent are possible if one embraces the notion of tuning and customizing the processor to the application. He went on to explain that doing this by hand is very difficult and that’s why Codasip invested in three areas: The tools, the methodology and a range of IP cores that are ready for customization. On that last point, Mike talked about the new 700 family that was announced at the show. This brings great flexibility across many applications and even has  technology in it that will thwart up to 70 percent of possible cyber-attacks. He ended by telling everyone to stop wasting time trying to optimize your design with an architecture that wasn’t meant to be modified. Call Codasip.

technology in it that will thwart up to 70 percent of possible cyber-attacks. He ended by telling everyone to stop wasting time trying to optimize your design with an architecture that wasn’t meant to be modified. Call Codasip.

Mike’s passion and commitment were quite clear. He did all this with one slide, that had, well, very little content.

Deep Computing: The First Phone Call from a RISC-V Pad

Yuning Liang, CEO of Deep Computing explained that his company develops applications across many markets, including personal computing, laptops, workstations and consumer electronics products as well, some of which could be seen around the show floor. The figure below summarizes the breadth of the company’s products.

With Tiffany’s help Yuning placed a phone call from a RISC-V pad live on stage, a first. Doing that in front of a large, live audience definitely shows the level of confidence Yuning has in his company and its products.

Esperanto Technologies: Generative AI Meets RISC-V

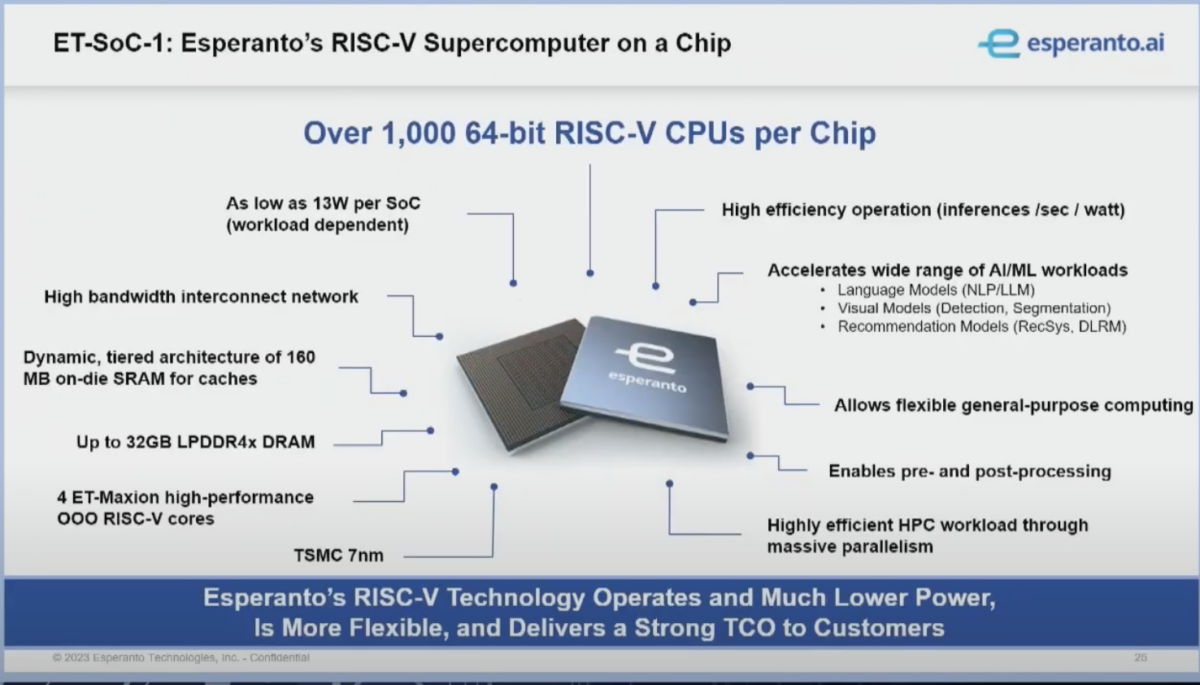

Craig Cochran is vice president of marketing and business development at Esperanto Technologies. He explained that the needs of high-performance computing and machine learning are actually converging. He went on to say that RISC-V was in a unique position to build the best converged HPC and ML systems.

Craig introduced Esperanto’s new RISC-V supercomputer on a chip, the ET-SoC-1. The device contains over 1,000 64-bit RISC-V CPUs per chip. The chip is very energy efficient and can be combined to make large systems. An architectural overview is shown below.

Craig ended with big news about a new application for this architecture. Esperanto is applying it to a new generative AI appliance for Ai inferencing. The performance and power efficiency are substantial, and the application space appears broad. This is one to watch for sure.

Semidynamics: Delivering Unfair Advantages with Tensor and Vector Unit Integration

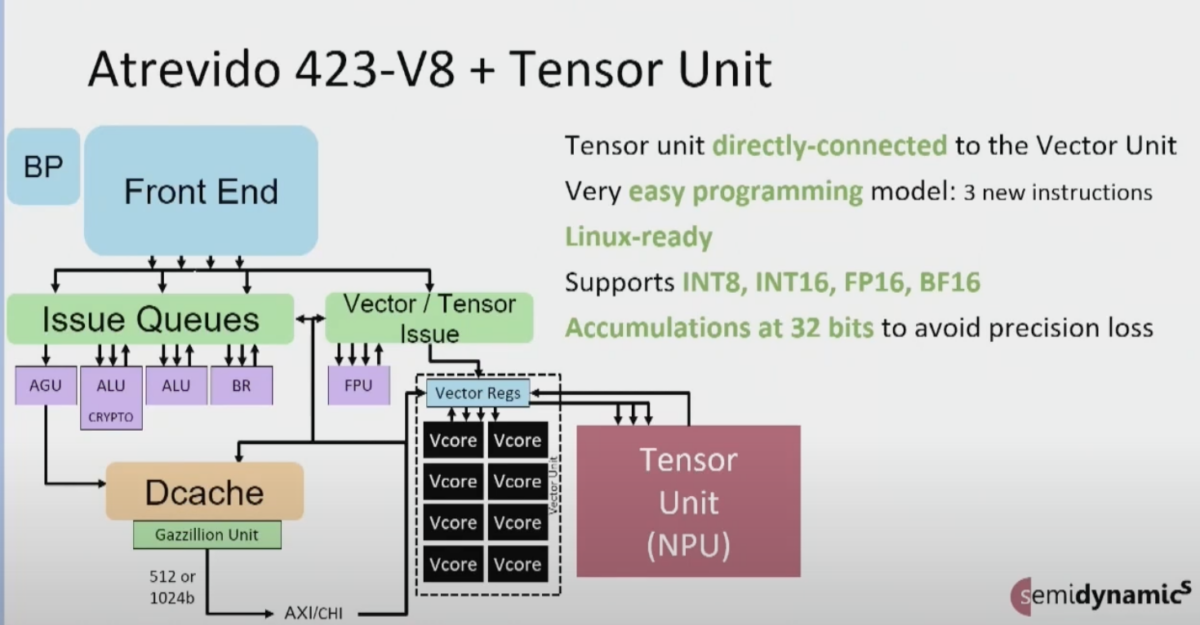

Roger Espasa, CEO and founder of Semidynamics explained the details of the company’s new design that directly connects a tensor unit with an existing vector unit. Roger gave one of the more detailed and technical presentations. The punch line is really one of efficiency and software compatibility.

AI processes will typically multiply matrices of data and perform operations based on the results. While Linux supports these concepts directly, a typical hardware implementation requires multiple operations and data movement to get it done. It’s far from elegant. Now, with the integrated architecture delivered by Semidynamics, vector operations are done in the tensor unit and the results are immediately available in the vector unit to support subsequent actions. It’s quite an elegant solution. The diagram below shows some details of the architecture.

This approach holds promise for great impact. Another one to watch.

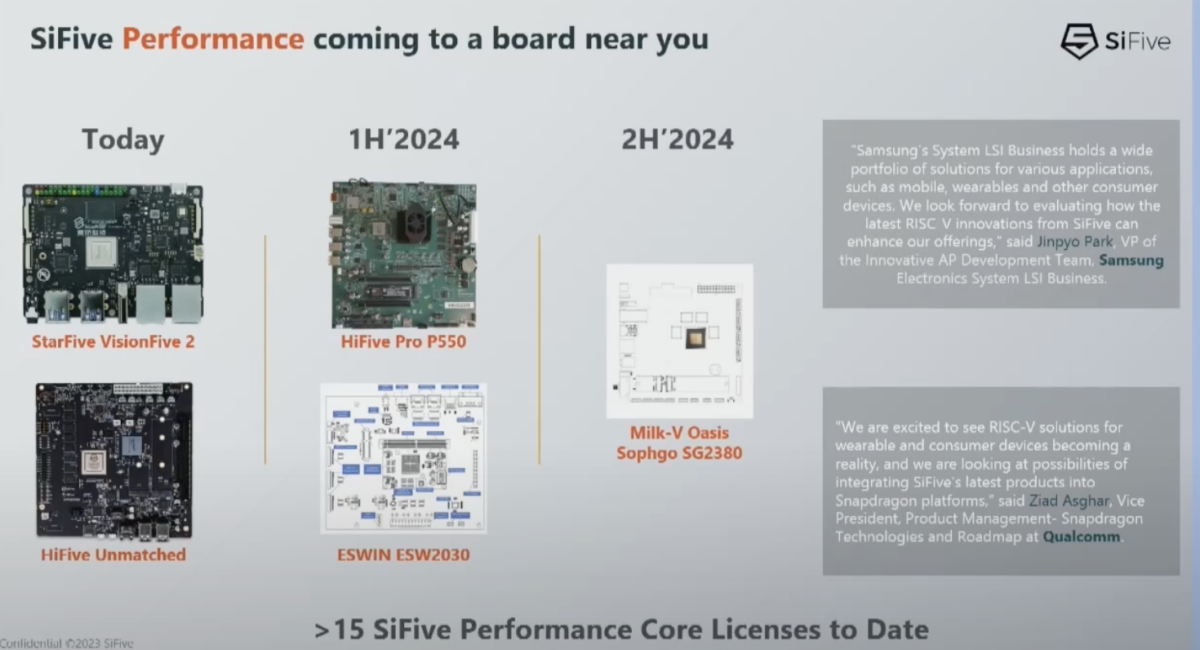

SiFive: Cores and Development Boards for All

Drew Barbier is senior director of product management at SiFive. He’s been with the company quite a while. Drew talked about the need for a complete solution, not just a RISC-V core. He explained that SiFive understands this need and is hard at work delivering complete solutions. Some of the items he discussed include:

- Coherent, heterogeneous system architecture

- RISC-V vector crypto extensions

- Hypervisor and IOMMU

- Advanced power management

- System security

The actual list is quite long, there’s a lot to deliver here. Drew then discussed the extensive development board program SiFive has underway. The company is working with its partners to deliver a wide variety of development boards that cover a lot of markets. Below is a summary of the program.

SiFive has clearly listened to its customers. Product support is quite extensive.

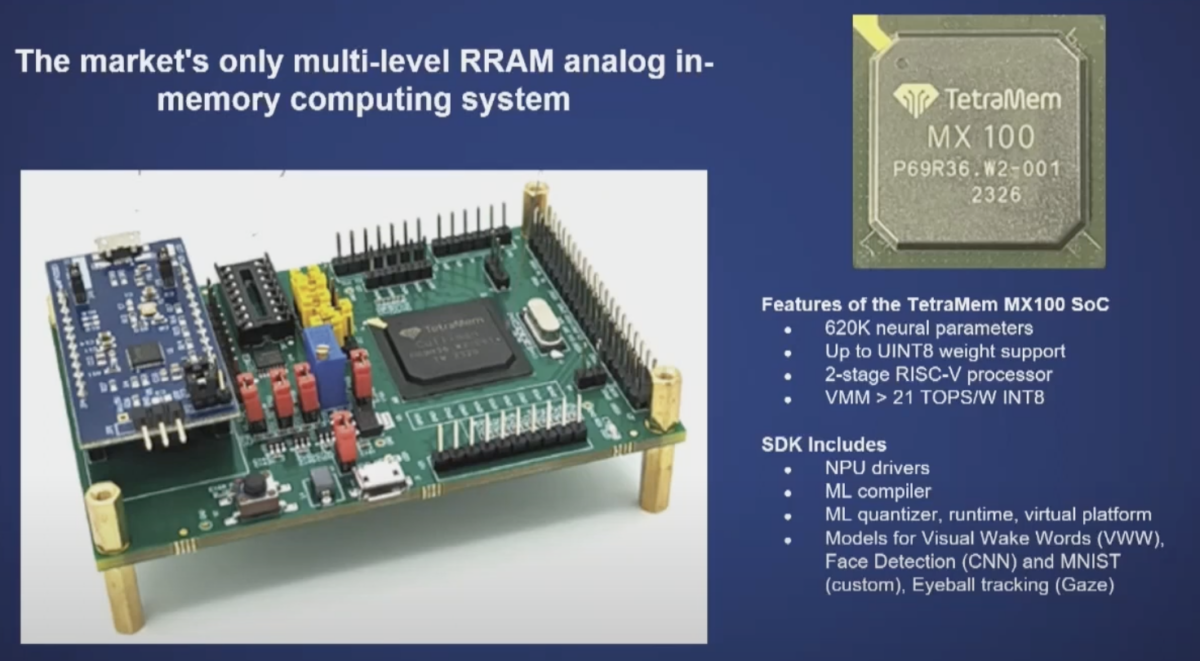

TetraMem: Welcome to a Revolution in the Physics of Computing

David George is head of global operations at TetraMem Inc. David talked about a new circuit element beyond the traditional capacitor, resistor and inductor. The memristor is the novel new circuit element at the core of TetraMem’s new product, the MX 100 which is the first commercial implementation of a memristor. The figure below summarizes some it its capabilities.

This device performs analog, in-memory compute on a RISC-V SoC. David explained that the analog devices are organized into neural processing units and use the memristor’s power in a unique way, eliminating the need for thousands of clock cycles. The result is a huge improvement in latency, power, and throughput. David went on to point out that this innovation required the application of skills across materials science, semiconductor processes and devices, circuit architecture, algorithms, and applications. This is a technological virtuoso performance, delivering a complete hardware and software solution for neural network inference for AI at the edge.

TetraMem is indeed orchestrating a revolution in the physics of computing. And the impact is growing with announced partnerships with Andes and Synopsys. Exciting stuff.

To Lean More

In a relatively short session, eight innovators presented potentially game-changing technology. This body of work could occupy a whole track at a conference like this. In this case, it was all covered in one short session. If you’d like to see the event, you can access a replay of it here. You can also learn more about RISC-V on SemiWiki here. The Launchpad Showcase highlights smaller company innovation – a great result from a growing RISC-V community.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.