- This event has passed.

Webinar: Trained Eyes on 64G UCIe: Scale Chiplet Integration for AI

Join us to hear firsthand from the innovators at Siemens and Alphawave Semi and learn proven practices to enhance your UCIe-enabled AI system performance!

The semiconductor industry is shifting rapidly from monolithic SoC design to chiplet-based systems. At the same time, AI compute workloads have pushed into petaflop-class speeds, demanding higher throughput from die-to-die (D2D) connectivity. 64G UCIe (Universal Chiplet Interconnect Express) delivers the performance, power, and area (PPA) advantages to meet the demands of tomorrow’s AI workloads. However, to achieve the performance for next-gen UCIe-based systems, design engineers face significant signal integrity challenges — from crosstalk and reflections to process variation.

This webinar will explore the emerging D2D connectivity applications, and the bandwidth demands that make 64G signaling a necessity. You’ll also learn how to:

- Optimize system performance, power, and area (PPA) with best-in-class IP

- Reduce design risks for advanced architectures with shift-left design methodologies

- Ensure design intent translates into reliable hardware via simulation-to-silicon correlation

Who Should Attend:

- Design engineers and system architects involved in designing, simulating, and validating chiplet-based systems — especially those tackling die-to-die (D2D) connectivity, UCIe integration, or seeking system-level PPA optimization.

Don’t miss out on this incredible chance to learn how to implement a comprehensive 64G UCIe design flow and participate in a live Q&A session! Register today to secure your spot.

Meet the speakers

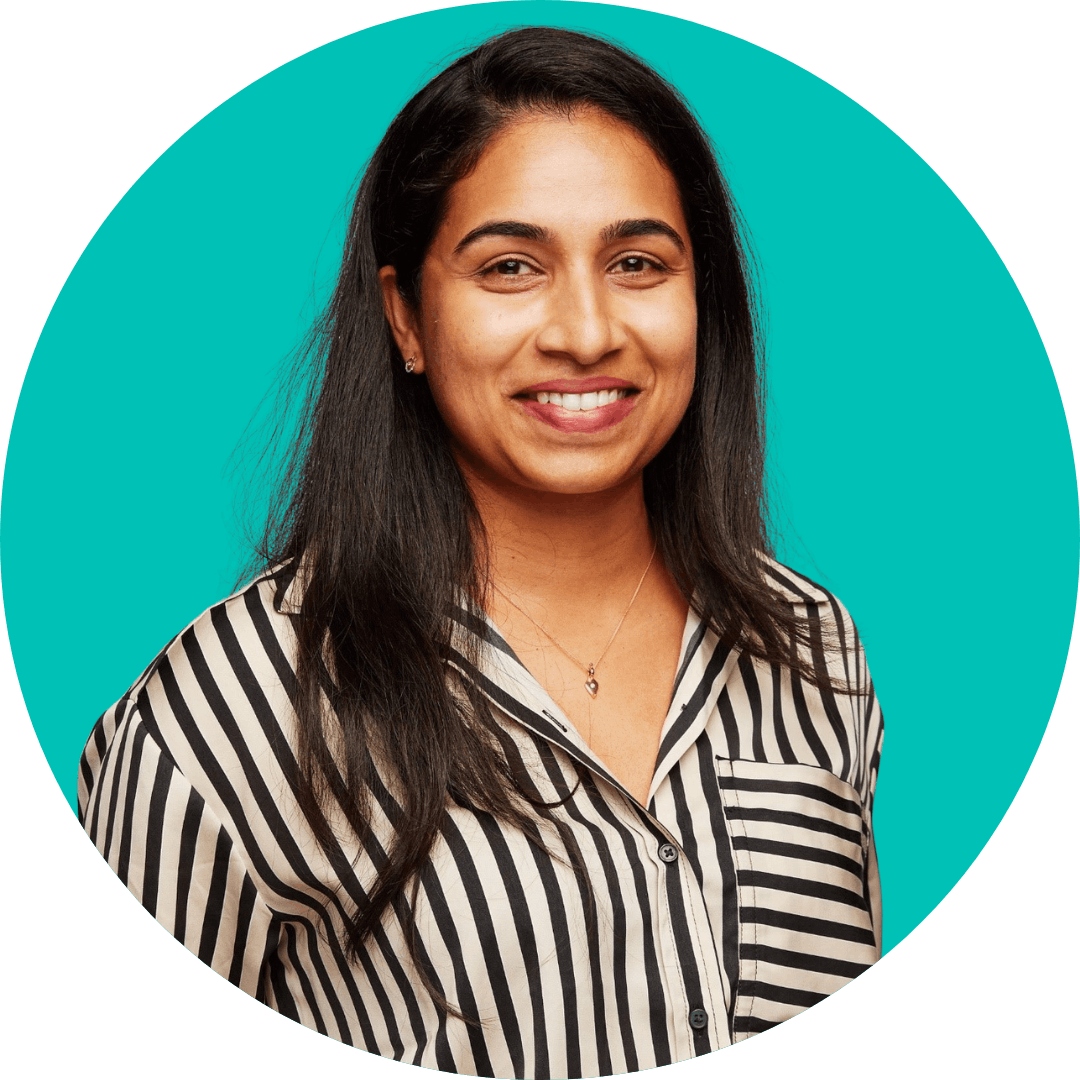

Alphawave Semi

Archana Cheruliyil

Principal Product Marketing Manager

Archana Cheruliyil is the Product Line Manager for HBM, D2D, and 3DIO IP at Alphawave Semi, where she drives the development of next-generation interface IP solutions and oversees marketing efforts. With a deep passion for identifying optimal solutions within the dynamic and complex landscape of AI systems, she works to address the evolving needs of customers. Archana is an invited speaker at conferences and panels on 3DIO interconnects and technology, where she shares insights on emerging trends and practical implementations in advanced packaging.

Previously, Archana served as the IP Strategy and Planning Lead at Intel Corporation, where she played a key role in defining and advancing the interface IP roadmap for both the Client and Data Center business units. She has over a decade of experience in analog mixed-signal design, specializing in high-speed clocking circuits, and has successfully led a matrixed engineering team to deliver cutting-edge IP on leading-edge process nodes.

Archana holds a Master of Science in Electrical Engineering (MSEE) from the University at Buffalo.

Siemens

Bryan McDevitt

Applications Engineer,

Bryan McDevitt is an Applications Engineer at Siemens EDA, where he has spent 18 years supporting board- and package-level simulations with the HyperLynx suite of tools. Before moving into applications engineering, he worked as an electrical engineer designing single board computers.

Siemens

Kendall Hiles

Sr. Product Specialist – 3D IC Packaging flow

Kendall Hiles is a Sr. Product Specialist for the 3D IC Packaging flow at Siemens Digital Industries Software, bringing over 40 years of comprehensive experience in electronics design and test engineering. He specializes in customizing EDA tools and developing sophisticated automated workflows that effectively bridge traditional design methodologies with cutting-edge packaging innovations and advanced semiconductor technologies. Throughout his extensive career, his expertise encompasses developing robust batch processing capabilities and establishing streamlined handoffs across the entire IC Packaging toolchain, ensuring efficient data flow and maintaining design integrity throughout complex multi-tool workflows. His current work includes pioneering automation solutions for creating system-level test vehicle daisy chains specifically designed for chiplet-based architectures, as well as developing comprehensive automated analysis capabilities for DC Drop power analysis, Loop PDN analysis, and high-frequency S-Parameter extractions for advanced IC package designs. Kendall’s innovative approaches have significantly improved design productivity while reducing time-to-market for complex packaging solutions, making him a recognized expert in the intersection of traditional PCB design and modern IC packaging technologies.

A Century of Miracles: From the FET’s Inception to the Horizons Ahead