USB 3 protocol is now height years old, but USB 3.1 is much more recent (2014). The adoption behavior for USB protocol is unique, as USB 2.0 bandwidth (480 Mbps) is largely enough for certain applications. Nevertheless we have seen the sales for USB 3 IP passing the USB 2 in value during 2014, and the total USB IP segment becoming the largest of interfaces segment in 2015.

USB 3.x IP sales are constantly growing and we can expect applications relying on USB 3.0 (5 Gbps) to upgrade to USB 3.1 (10 Gbps). When deciding to integrate complex interface IP running at 10 Gbps, the first question coming in the selection process is: has this IP passed the qualification? Because we are talking about interface IP, you a priori don’t know the quality of the USB IP your chip will interface with. The only way to make sure that both function will smoothly communicate is the qualification process, supported by USB-IF. Synopsys has announced that their DesignWare USB 3.1 controller and PHY passed all protocol, electrical and interoperability tests to become the first IP to achieve USB-IF certification. As we will see in this paper, this long process is all but an easy trip.

USB 3.1 Gen 2 significantly increases the effective data rate to 10 Gbps for the ubiquitous USB protocol, while maintaining backward compatibility with USB 3.0 and 2.0. USB 3.1, in combination with USB Type-C and Power Delivery. We have to keep it mind that a modern (interface) IP is no more a simple bunch of source code RTL: complete USB 3.1 solution includes controller, PHY, verification IP, IP subsystems, IP prototyping kits and IP software development kits.

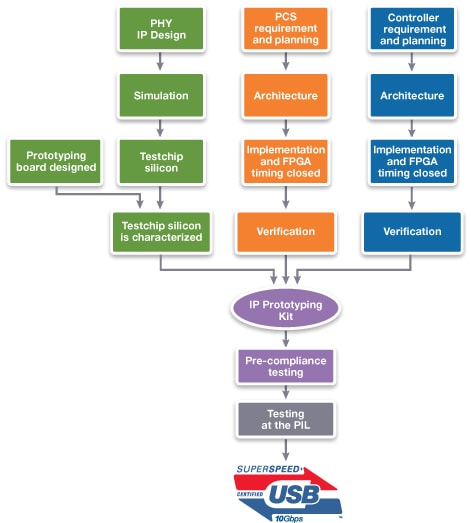

Controller: The preparation for compliance testing starts together with the project schedule definition, and will apply to every phase of the controller development, helping to drive the schedule and collaboration process with the engineering teams involved in deliverables such as the PHY, simulation verification IP (VIP) models and software drivers. The ASIC design engineers task become a compliance-driven design approach.

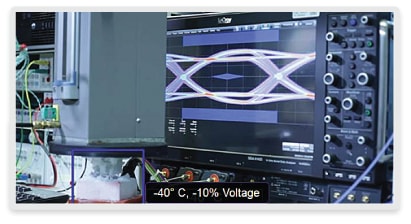

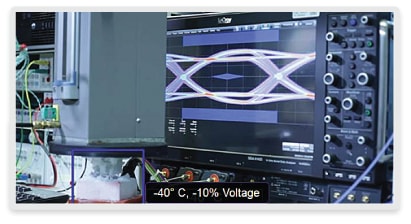

PHY: The PHY testchip silicon will be exhaustively verified within Synopsys laboratories before going to certification, thanks to the PHY architecture which allows for the transmitter (TX) and receiver (RX) of the PHY to be operated standalone, with pattern generators and pattern matchers incorporated into the PHY itself.

Verification IP (VIP): The verification phase of a complex protocol such as USB 3.1 Gen 2 represents a paramount effort where constrained random regression approaches can take considerable time to go through thousands upon thousands of coverage points. Parallel efforts focused on direct test scenarios that address compliance test simulation environments are actively sought after to improve the process. For example, the link layer compliance test is a perfect candidate for writing direct test cases.

IP Prototyping Kit: FPGA-based prototyping provides cycle-accurate, high-performance execution and real-world interface connectivity. When the controller has been integrated in FPGA, the PHY Testchip has been mounted on the same board, the full IP Prototyping Kit, pre-compliance testing can begin.

Although the Synopsys methodology minimizes roadblocks and accelerates processes, it is Synopsys’ array of industry-tested tools and prototyping environments, along with its experienced team, that results in IP validation, verification, and compliance (see above Figure). Synopsys has proven its methodology by being the first IP companies to achieve certification for USB 3.1 Gen2.

The DesignWare USB 3.1 Controller IP implements power management features, including standard USB power savings modes and controller hibernation. DesignWare USB 3.1 PHYs consume less than 50 mW power at 10 Gbps speeds in 14/16-nm FinFET process technologies. The IP supports the IEEE 1801 standard Unified Power Format (UPF) for low-power SoC design flows. The controllers are backward-compatible with DesignWare USB 3.0 software stacks and device class protocols. No doubt that the complete USB 3.1 solution from Synopsys will allow the company to keep his leading position in USB IP segment with more than 80% market share in 2015!

– See more about Synopsys certification strategy and process at: http://www.synopsys.com/Company/Publications/DWTB/Pages/dwtb-challenges-usb-certification-2016q2.aspx#sthash.j0wOVnaV.dpuf

– Synopsys PR about sertification: Synopsys’ 10 Gbps USB 3.1 IP First to Pass USB-IF Certification

From Eric Esteve from IPNEST

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.