By Omar Elabd

As semiconductor designs move below 7 nm, parasitic effects—resistance, capacitance and inductance—become major threats to IC performance and reliability, often hiding where netlist reviews cannot reach. Design teams need advanced visualization tools like heat maps, layer-based analysis and direct layout correlation to spot and fix these invisible problems fast. Using a structured, multi-level workflow and an integrated EDA tool environment helps teams cut debug time and boost first-pass silicon success.

Seeing what the netlist cannot reveal

“Why does the simulation say this will work, but the chip fails every time in silicon?” If you’ve ever asked this question after weeks of painstaking debug, you are not alone. For IC designers working at the bleeding edge—below 7 nm, in billions of transistors and stacked 3D structures—the hardest problems are often the ones you can’t see. Invisible enemies lurk in every layout: resistance, capacitance and inductance effects that don’t manifest in your schematic, but can dominate performance and threaten reliability.

Modern parasitic problems are no longer minor corrections—they are decisive factors. Once you are working at the 5 nm node, hidden parasitics can account for more than half of total signal delay, compared to just one-tenth at older process technologies. Industry analysis reveals the critical impact: parasitic-related failures in advanced silicon designs can cost development teams weeks of debugging effort per incident.

This is the reality driving innovative approaches to visualization and analysis that help engineers see what a netlist alone cannot. By putting “eyes” on parasitics, designers can finally move from educated guesswork to precise solutions.

The unseen challenge: How parasitics threaten design success

Parasitic effects are electrical interactions that arise from the physical realities of semiconductor fabrication—unintentional resistance, capacitance and inductance generated by routing, stacking and proximity of metal structures. These are not intrinsic parts of the schematic, but unwelcome guests within every layout.

Their impact grows exponentially with process scaling and architectural complexity. For example:

- Differential pairs and high-speed signaling: PCIe, DDR and SerDes interfaces depend on perfectly matched signal paths. Even a small mismatch in parasitic capacitance—just 5%—can trigger significant bit errors or total link failures. Identifying and fixing these subtle imbalances can require weeks of repeated layout analysis.

- RF and high-frequency circuits: Circuits operating above 20 GHz are exceedingly sensitive to parasitics, such as inductive resonances in ground connections that can degrade transceiver fidelity by 30% or more.

- Complex 3D architectures: FinFET and GAAFET structures introduce multi-layer parasitic effects that aren’t visible in traditional 2D reviews, making timing closure a moving target.

As stakes grow, traditional netlist-only methods are insufficient. The question becomes: How can engineers visualize, analyze and target the real root causes of performance failure within billions of intricate layout elements?

Elevating parasitic analysis: Making the invisible visible

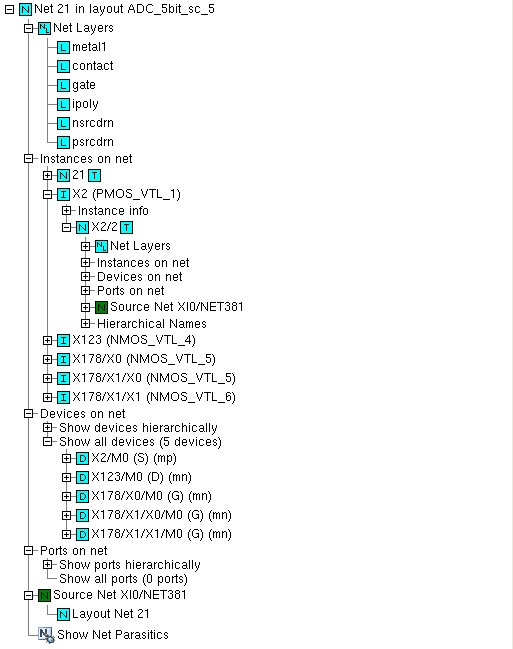

To meet these needs, modern design workflows are evolving towards more comprehensive visualization and analysis techniques. Instead of reviewing static reports or text-based netlists, engineers use graphical representations that illuminate problem areas, quantify their impact and correlate electrical anomalies directly to their physical structures. A basic net visualization is illustrated in figure 1.

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig1-net-level-visualization.jpg)

- Heat maps: Intuitive color gradients instantly reveal high-resistance or high-capacitance hotspots.

- Layer-based views: Designers can track parasitic paths across stacked metal and via layers, uncovering issues that escape 2D inspection.

- Component-level highlighting: Engineers can pinpoint exactly which polygon or segment contributes to a problematic parasitic value, enabling precise fixes rather than broad re-designs.

- Filtering and sorting: The ability to focus on specific nets, layers or parasitic types streamlines the hunt for critical contributors.

- Direct layout correlation: Electrical values align with real physical structures, reducing the disconnect between simulation and manufacturing reality.

The value of visualization is not just in finding problems, but in reducing time and uncertainty. Broad overview capabilities combined with precise local analysis enable teams to move quickly from symptom to root cause—and from root cause to targeted solution.

Multi-level debugging: A hierarchical approach to effective analysis

Advanced parasitic workflows employ a structured, multi-level strategy, guiding users from global assessment to pinpoint measurements:

- Global net analysis: Identify potentially problematic nets and regions across the entire chip.

- Layer interaction review: Track how each net interacts with the multi-layer stack, uncovering inter-layer coupling or bottlenecks. Figure 2 shows an example layer-based view.

- Component-level inspection: Isolate individual parasitic values and their exact physical locations.

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig2-layer-based-analysis.jpg)

Categorizing and targeting parasitic impacts

A powerful parasitic analysis solution organizes extraction results into structured categories (figure 3) that reflect real physical properties:

- Resistance and inductance sorted by layer, because these effects depend heavily on geometry and routing.

- Coupling capacitance and mutual inductance categorized by net, aligning with how signals cross-talk and interact in densely packed circuits.

This enables designers to sort, filter and prioritize the highest-risk contributors. For example, sorting for maximum capacitance between nets on a SerDes channel highlights potential sources of bit errors faster than a manual scan through pages of raw numbers.

Mapping and modifying physical structures for performance gains

Visualization environments bridge the divide between electrical anomalies and their specific physical causes. By highlighting polygon segments that drive high resistance, as shown in figures 3 and 4, engineers can immediately spot bottlenecks, narrow traces or problematic vias.

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig3-resistance-layout.jpg)

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig4-p2p-resistance.jpg)

For capacitance, visualizing exact segments responsible for coupling (figure 5) or intrinsic (figure 6) effects means improvements can be focused—such as modifying only the problem edge instead of rerouting the entire net.

![[white paper] Parasitic Analysis Figures [white paper Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig5-coupling-cap.jpg)

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig6-intrinisic-cap.jpg)

Color-driven detection: Heat maps reveal hotspots

Heat maps are a powerful tool for visually identifying and prioritizing parasitic issues. Color-coded gradients transform raw data into intuitive displays: red for problematic intensity, green or blue for optimal performance (figure 7).

![[white paper] Parasitic Analysis Figures [white paper] Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig7-Intrinsic-cap-heatmap.jpg)

Reporting and connectivity: Detailed insights for optimization

Efficiently optimizing net performance depends on access to structured information, not just raw extraction data. Report-driven approaches present the hierarchy, connectivity and physical attributes of every net, along with all associated devices, ports and layer usage (figure 8).

Switching between hierarchical and flat views helps teams analyze both the design logic and implementation details, all linked directly with the layout.

Parasitic-aware simulation: Unifying analysis and validation

Bringing schematic probing and full parasitic analysis into a single environment removes traditional workflow barriers (figure 9). Designers can launch simulations that account for every extracted parasitic effect—directly from the schematic, with results correlated to both physical layout and electrical performance.

![[white paper] Parasitic Analysis Figures [white paper] Parasitic Analysis Figures](https://semiwiki.com/wp-content/uploads/2025/10/Fig9-unified-environment.jpg)

Siemens Calibre: Solving the challenge with industry-leading visualization

The visualization and analysis methodologies described above are brought to life in Siemens Calibre extraction and debug solutions. Leading-edge design teams worldwide rely on Calibre xRC, Calibre xACT and Calibre xACT 3D for performance-accurate parasitic extraction, backed by Calibre Interactive and Calibre RVE for advanced, user-friendly visualization.

Calibre’s multi-level approach delivers measurable gains: users report up to 50% reductions in parasitic debugging time, 35% improvements in first-pass silicon success and a 25% increase in critical path timing performance. Structured workflows start with broad overview and drill down to component-level fixes, leveraging heat maps, filtering, and direct layout correlation, all in a unified environment.

What sets Calibre apart is its deeply integrated environment: from schematic probing and parasitic extraction to simulation, every step is streamlined. Engineers can highlight specific nets, layers or physical structures, instantly visualize hotspots and generate automated reports for compliance or ongoing optimization. This combination of visualization, quantification and interaction empowers rapid debug and smarter design decisions.

For organizations designing high-speed interfaces, RF circuits or complex multi-layer SoCs, Calibre offers the flexibility to build custom workflows that emphasize capacitance mitigation, resistance targeting or specialized 3D analysis as needed. Its modular framework adapts to each project’s unique challenges, supporting continuous innovation as process nodes scale down and design architectures evolve.

Conclusion: Seeing the future of IC performance

In the relentless drive to smaller nodes and greater circuit complexity, invisible parasitic effects have become major roadblocks to performance, reliability and time-to-market. By adopting visualization-rich analysis and interactive debugging, IC design teams gain the clarity needed to see, understand and solve what traditional netlists alone never reveal.

The future of high-performance IC design depends on making the invisible visible—transforming data into actionable insight, and insight into proven results. With tools like Siemens Calibre leading the way, design teams can meet the challenge and realize the full potential of modern semiconductor innovation.

Ready to dive deeper into strategies for tackling hidden parasitic effects in advanced IC design?

Download the full technical paper, “Beyond the netlist: Visualizing the invisible enemies of IC performance,” to learn more.

About the author:

Omar Elabd is a Product Engineer at Siemens EDA, supporting Calibre extraction products. Based in Cairo, Egypt, Omar is an honors graduate of The American University Cairo with a major in Electronics and Communication Engineering along with a minor in Business Administration. Omar specializes in developing customer-specific flows for Calibre extraction tools and focuses on expanding the edge of current technology to meet evolving industry demands. He can be reached at omar.elabd@siemens.com

Also Read:

Protect against ESD by ensuring latch-up guard rings

Something New in Analog Test Automation

Tessent MemoryBIST Expands to Include NVRAM

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.