The concept of built-in self-test for electronics has been around for a while. An article in Electronic Design from 1996 declared that, “built-in self-test (BIST) is nothing new.” The memory subsystem is a particularly large and complex part of any semiconductor design, and it’s one that can be particularly vexing to test. Design teams have therefore applied the concepts of BIST to memories for quite a while as a result. Memory BIST has many advantages including better reliability, reduced manufacturing costs, and enhanced system performance. The complexity of implementing an effective memory BIST strategy has gotten quite challenging, however. The huge size and performance demands of memory systems contributes to this, as does the additional complexity of 3D IC design.

Siemens Digital Industries Software has been developing the Tessent™ MemoryBIST software and IP to deliver a complete solution for at-speed test, diagnosis, repair, debug and characterization of silicon memories of all types. The ability to address this broad class of problem with one comprehensive solution provides significant benefits. This platform has recently been extended to handle the unique requirements of embedded non-volatile RAM, or NVRAM. Since embedded NVRAM use is on the rise, this is a significant addition. Let’s examine the footprint of what Siemens delivers with a special focus on how Tessent MemoryBIST expands to include NVRAM.

Tessent MemoryBIST Overview

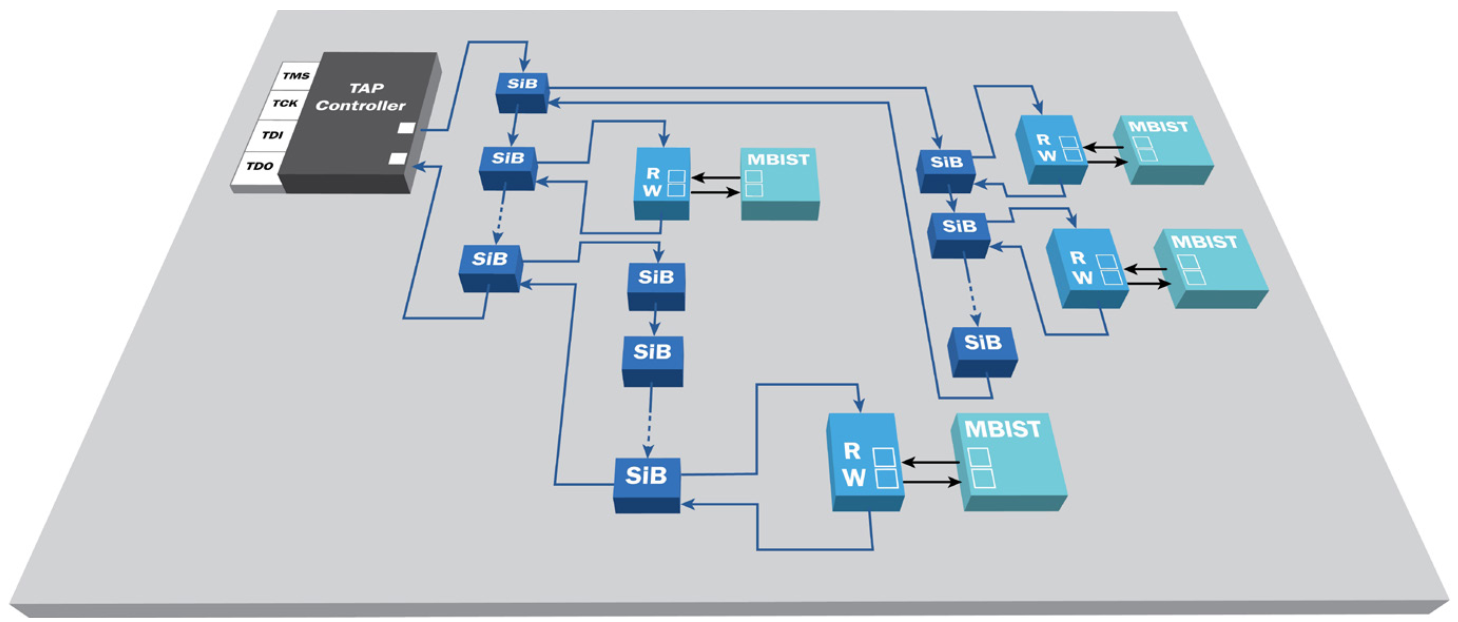

Some of the reasons that this platform is the Industry-leading solution for memory built-in self-test include its hierarchical architecture that enables the addition of built-in self-test and self-repair capabilities at both the individual core level and the top level. Both software and enabling IP are included.

The system delivers on-chip generated test vectors to memories at application clock frequencies. Tessent MemoryBIST controllers are configurable to support a variety of memory types, as well as a range of memory timing interfaces and port configurations. These are accessed and controlled through an IEEE 1687-2014 (IJTAG) network. This highly configurable network can access all Tessent IP and support any third-party IJTAG-compliant instruments. There is a lifecycle management aspect to this as well, since controllers can be accessed throughout the life of the device, including manufacturing test, silicon debug and in-system test. The figure below illustrates the hierarchical Tessent MemoryBIST infrastructure.

There are many benefits provided by a system like this. Here are some:

- Flexible and automated BIST IP integration, access network integration and pattern validation shorten time-to-market

- Resource sharing and flow integration with Tessent LogicBIST and Tessent TestKompress reduce overall DFT cost and increase defect coverage

- The option to use field programmable algorithm specifications allows complete control of test quality and test time trade-offs

- User controllable area and test time trade-off options enable product-specific test cost optimization

- On-chip global eFuse management and optional non-volatile memory test capability reduce overall manufacturing costs

- Desktop-based test debug and characterization speed time-to-market

- Customizable pass/fail criteria provided by the ECC option enhances yield and reliability

- Works with ECC detection/correction capabilities to safeguard against aging defects

A Look at NVRAM Support

Thanks in part to the ubiquitous use of AI workloads in just about every design, the need for embedded NVRAM is growing significantly. While Flash has been the go-to approach for years, this technology doesn’t scale to advanced process nodes and so there are several new NVRAM technologies entering the market.

NVRAMs have very different test criteria and requirements, and so the need for BIST automation here is quite significant. That’s why the recent expansion of Tessent MemoryBIST to include NVRAM is so important. I had the opportunity to speak with Etienne Racine, the Product Manager for Tessent MemoryBIST at Siemens Digital Industries Software. Etienne has been working on silicon test solutions at Siemens and at Mentor before that for almost 18 years. Prior to Siemens and Mentor, he spent over a decade working on advanced test solutions, so Etienne brought a wealth of knowledge to the discussion.

Etienne explained that until recently there has been no well-developed BIST support for NVRAMs. This is why the additional capabilities of the Tessent suite are significant. We discussed access protocols and Etienne explained that the commands to operate embedded NVRAMs are quite different than those for embedded SRAMs. This means that the way BIST interfaces to the NVRAM must be changed. We also discussed the need to support trimming and trimming sequences. This process is similar to calibration.

He went on discuss the process of deployment of MRAMs, which is one of the newer embedded NVRAM technologies designed to replace Flash. For MRAMs, a trimming, or calibration step must be done before the device can be reliably used. The Tessent MemoryBIST NVM option provides these capabilities in an automated way. He also discussed the ability to define the required waveforms needed to test new NVRAM technologies. These waveforms can be described in the Tessent platform, paving the way for more efficient BIST strategies.

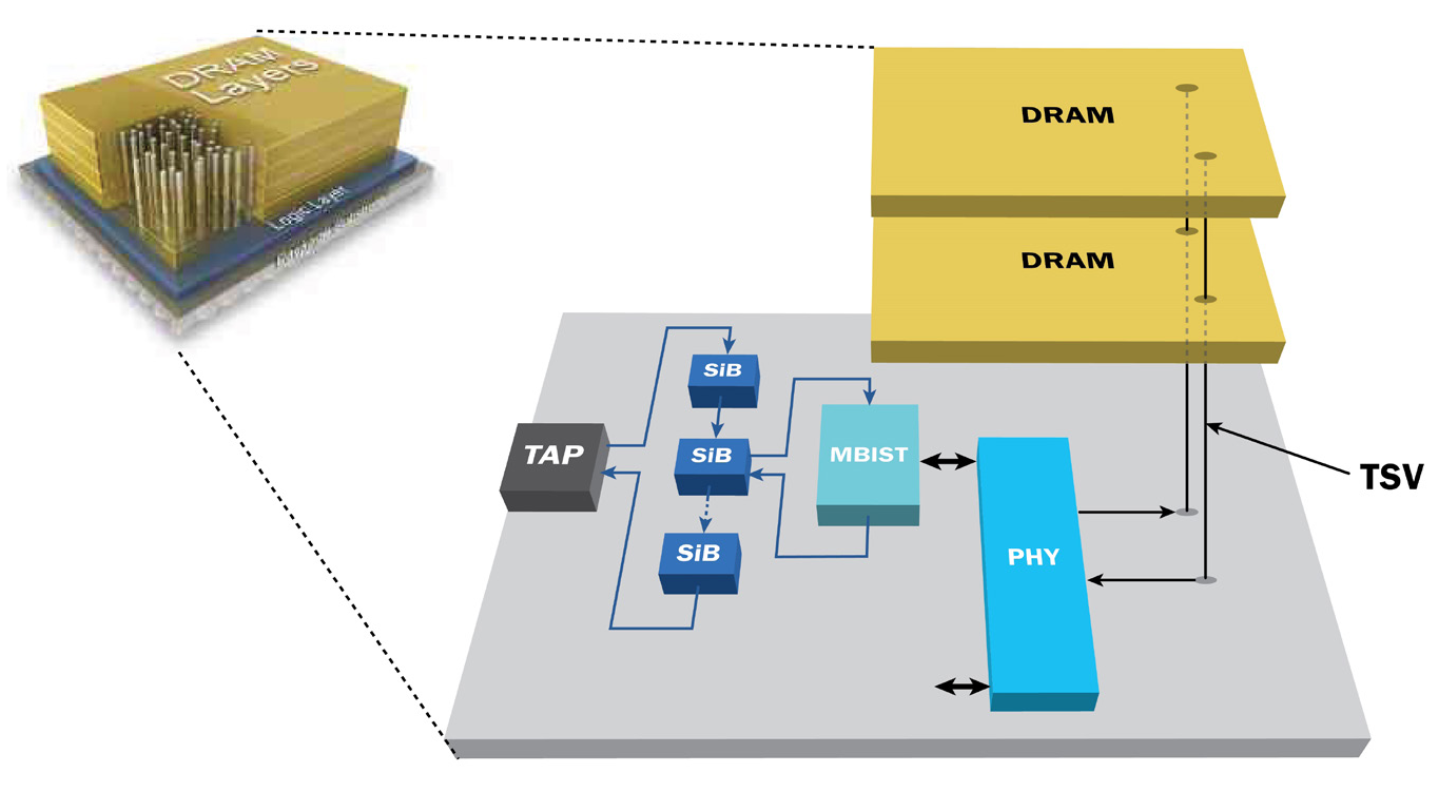

Looking ahead, Tessent MemoryBIST also provides support for testing memories that are external to the device containing the BIST IP. Support is provided for both stand-alone memory packages at the board level and 2.5/3D packages consisting of one or more memory dies stacked on top of a separate logic die. This strategy is summarized in the diagram below.

To Learn More

My conversation with Etienne touched on many topics. There are a lot more capabilities delivered by the Tessent MemoryBIST software and IP. You can find many well packaged solutions to your MBIST requirements here. The good news is there is a comprehensive overview of the platform available. You can access your copy of Tessent MemoryBIST, memory self-test, repair and debug here. And that’s how Tessent MemoryBIST expands to include NVRAM.

Also Read:

Smart Verification for Complex UCIe Multi-Die Architectures

Orchestrating IC verification: Harmonize complexity for faster time-to-market

Perforce and Siemens at #62DAC

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.