I haven’t made a secret of the fact that I maintain Oasys Design System’s website. So I had a small task yesterday of adding Qualcomm to the list of customer logos that cycle through on the home page. It is a pretty impressive list including Juniper Networks, Netlogic Microsystems, Texas Instruments and ST Microelectronics. Oh yes, and Xilinx, who have licensed the technology but haven’t publicly said anything about what they are doing with it.

I haven’t made a secret of the fact that I maintain Oasys Design System’s website. So I had a small task yesterday of adding Qualcomm to the list of customer logos that cycle through on the home page. It is a pretty impressive list including Juniper Networks, Netlogic Microsystems, Texas Instruments and ST Microelectronics. Oh yes, and Xilinx, who have licensed the technology but haven’t publicly said anything about what they are doing with it.

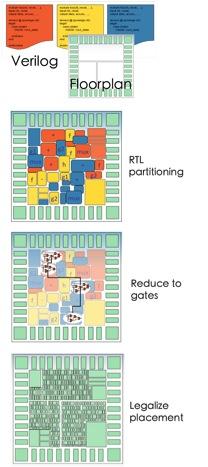

Here’s the elevator summary of what is different about Oasys’s Chip Synthesis from traditional synthesis. Traditional synthesis, including Ambit BuildGates that the founders of Oasys worked on a decade ago, works by doing a quick and dirty conversion of the RTL to a gate-level netlist and then applying a powerful but slow optimizer to the netlist. Problem #1, it’s slow. Problem #2, you need to keep the entire netlist in memory the whole time which limits the size of design that can be handled. Chip Synthesis takes almost the opposite approach, and puts most of the intelligence into how to turn RTL into optimized gates a small piece at a time. Further optimization is done, not by working directly on that netlist as in traditional synthesis, but by returning to the RTL level with a bit more information on the local constraints and generating a new small peiece of netlist from a small piece of RTL.

Here’s the elevator summary of what is different about Oasys’s Chip Synthesis from traditional synthesis. Traditional synthesis, including Ambit BuildGates that the founders of Oasys worked on a decade ago, works by doing a quick and dirty conversion of the RTL to a gate-level netlist and then applying a powerful but slow optimizer to the netlist. Problem #1, it’s slow. Problem #2, you need to keep the entire netlist in memory the whole time which limits the size of design that can be handled. Chip Synthesis takes almost the opposite approach, and puts most of the intelligence into how to turn RTL into optimized gates a small piece at a time. Further optimization is done, not by working directly on that netlist as in traditional synthesis, but by returning to the RTL level with a bit more information on the local constraints and generating a new small peiece of netlist from a small piece of RTL.

As Jaggy Rao of TI said:RealTime Designer is not just an incremental improvement, it is truly the next generation of physical synthesis for complex, multi-million gate designs at leading-edge process nodes.

If you want the 500 storey building elevator version of how Chip Sythesis works, there is a white paper here.

Oh yes, and if you didn’t go to DAC, or you did go but you missed it, then have a good laugh at the 2011 Oasys DAC video.

Share this post via:

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center