You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 1

[name] => Uncategorized

[slug] => uncategorized

[term_group] => 0

[term_taxonomy_id] => 1

[taxonomy] => category

[description] =>

[parent] => 0

[count] => 186

[filter] => raw

[cat_ID] => 1

[category_count] => 186

[category_description] =>

[cat_name] => Uncategorized

[category_nicename] => uncategorized

[category_parent] => 0

[is_post] =>

)

Don’t forget the SpringSoft Community Conferences next week in Austin on Tuesday and in San Jose on Thursday. There is no charge and you even get a free lunch (see “no such thing as…”).

The morning in Austin is focused on functional closure and how to leverage SpringSoft’s verification technology… Read More

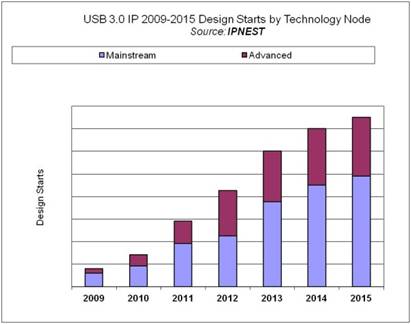

Using the “Diffusion of Innovation” theory, we have built a forecast for the market of USB 3.0 IP in 2011-2015. In this new version of the report, we have inserted the actual revenues generated by USB 3.0 IP from different vendors, for 2009 and 2010, and reworked the 2011-2015 forecast. Initially, we had expected this IP market to … Read More

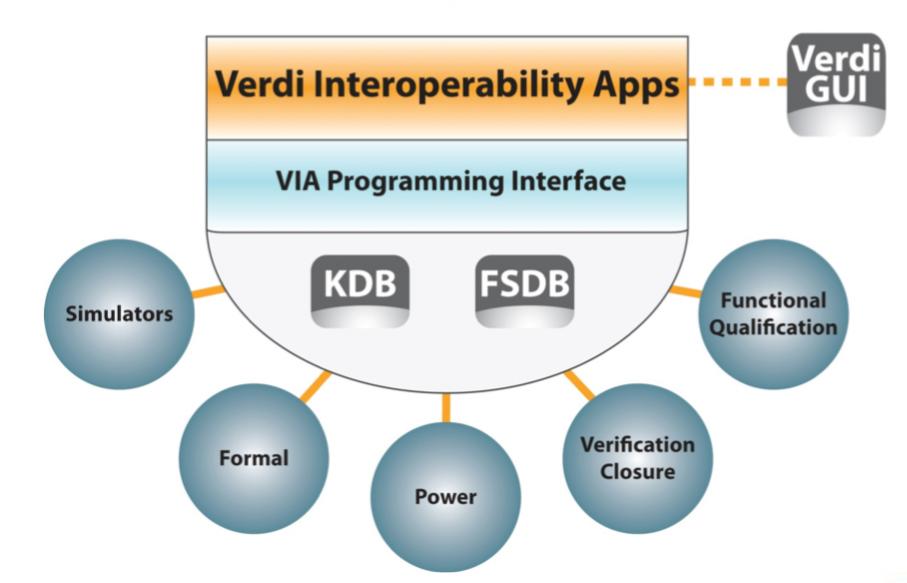

Verdi is very widely used in verification groups, perhaps the industry’s most popular debug system. But users have not been able to access the Verdi environment to write their own scripts or applications. This means either that they are prevented from doing something that they want to do, or else the barrier for doing it is… Read More

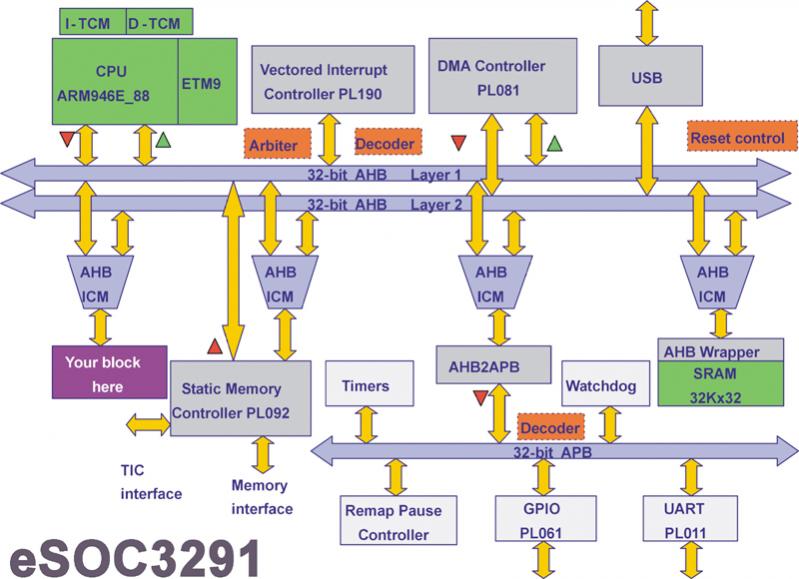

I was at the first half of Magma’s Silicon One event yesterday. The first keynote was by Rajeev about the environment for SoC designs, especially fabless startups, and Magma’s role going forward. More about that later. The other keynote was Jack Harding, CEO of eSilicon. As usual Jack did his presentation without … Read More

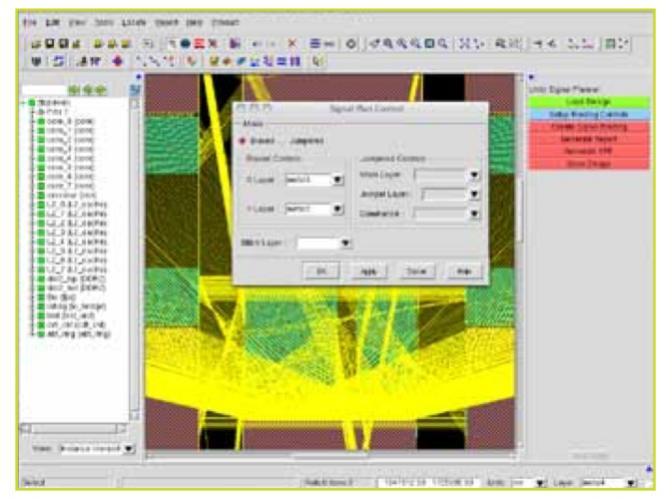

It is no secret that custom ICs are getting larger and more complex and this has driven chip design teams to split up into smaller teams to handle the manual or semi-automated routing of the many blocks and hierarchical layers that go to make up such a design. These sub-teams don’t just need to handle the routing within their own block(s)… Read More

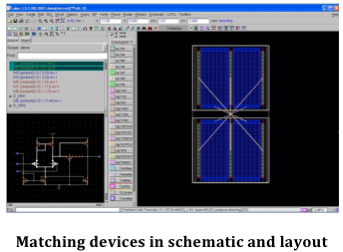

Over the years there has been a lot of standard creation in the IC design world to allow interoperability of tools from different vendors. One area of recent interest is interoperable constraints for custom IC design. Increasingly, analog design layout is becoming more automated. Advanced process nodes require trial layouts… Read More

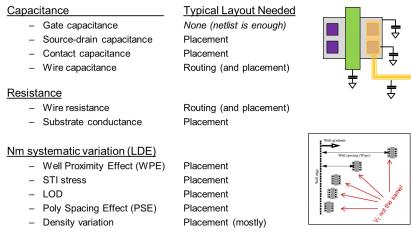

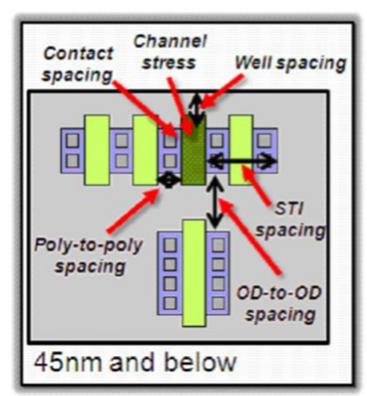

As analog and mixed-signal designers move to very advanced geometries, they must grapple with more and more complex considerations of the silicon. Not only do nanometer CMOS devices have limitations in terms of analog-relevant characteristics such gain and noise performance, but they also introduce new sources of variation… Read More

AMS design flows can follow a traditional path or consider trying something new. The traditional path goes along the following steps:

[LIST=1]

Design requirements

Try a transistor-level schematic

Run circuit simulation

Compare the simulated results versus the requirements, re-size the transistors and go back to step 3 or …

Read More

Earlier in the week I met with Phil Bishop, who is the corporate VP of worldwide marketing at Magma.

I started by asking him where he came from. He originally started as a designer at Motorola in microprocessors and microcontrollers. Then he moved to Silicon Compiler Systems (remember them?) who ended up being acquired by Mentor.… Read More

Analog has always been difficult, a bit of a black art persuading a digital process to create well-behaved analog circuits, capacitors, resistors and all the rest. In the distant past, we would solve this by putting the analog on a separate chip, often in a non-leading-edge process. But modern SoCs integrate large amounts of digital… Read More

Things From Intel 10K That Make You Go …. Hmmmm