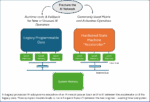

At Quadric we do a lot of first-time introductory visits with prospective new customers. As a rapidly expanding processor IP licensing company that is starting to get noticed (even winning IP Product of the Year!) such meetings are part of the territory. Which means we hear a lot of similar sounding questions from appropriately… Read More

Semiconductor Intellectual Property

Mixel at the 2025 Design Automation Conference #62DAC

Mixel, Inc., a leading provider of mixed-signal interface IP, will exhibit at booth #2616 at Design Automation Conference (DAC) 2025 on June 23-25. The company will demonstrate its latest customer demos featuring Mixel’s MIPI PHY IP and LVDS IP. Mixel’s customers include many of the world’s largest semiconductors and system… Read More

Analog Bits at the 2025 Design Automation Conference #62DAC

Analog Bits attends a lot of events. I know because I see them a lot in my travels. Lately, the company has been stealing the show with cutting-edge analog IP on a broad range of popular nodes and a strategy that will change the way design is done. Analog Bits is quietly rolling out a new approach to system design. One that delivers a holistic… Read More

Arm Reveals Zena Automotive Compute Subsystem

Last year Arm announced their support for standards-based virtual prototyping in automotive, along with a portfolio of new AE (automotive enhanced) cores. They also suggested that in 2025 they would be following Arm directions in other LOBs by offering integrated compute subsystems (CSS). Now they have delivered: their Zena… Read More

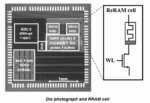

Relaxation-Aware Programming in ReRAM: Evaluating and Optimizing Write Termination

Resistive RAM (ReRAM or RRAM) is the strongest candidate for next-generation non-volatile memory (NVM), combining fast switching speeds with low power consumption. New techniques for managing a memory phenomenon called ‘relaxation’ are making ReRAM more predictable — and easier to specify for real-world applications.… Read More

Breker Verification Systems at the 2025 Design Automation Conference #62DAC

Breker Verification Systems Plans Demonstrations of its Complete Synthesis and SystemVIP Library and Solutions Portfolio

Attendees who step into the Breker Verification Systems booth during DAC (Booth #2520—second floor) will see demonstrations of its Trek Test Suite Synthesis and SystemVIP libraries and solutions portfolio.… Read More

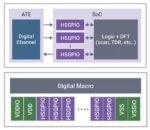

Synopsys Addresses the Test Barrier for Heterogeneous Integration

The trend is clear, AI and HPC is moving to chiplet-based, or heterogenous design to achieve the highest levels of performance, while traditional monolithic system-on-chip (SoC) designs struggle to scale. What is also clear is the road to this new design style is not a smooth one. There are many challenges to overcome. Some are … Read More

Anirudh Keynote at CadenceLIVE 2025 Reveals Millennium M2000

Another content-rich kickoff covering a lot of bases under three main themes: the new Millennium AI supercomputer release, a moonshot towards full autonomy in chip design exploiting agentic AI, and a growing emphasis on digital twins. Cadence President and CEO Anirudh Devgan touched on what is new today, and also market directions… Read More

Design-Technology Co-Optimization (DTCO) Accelerates Market Readiness of Angstrom-Scale Process Technologies

Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. … Read More

WEBINAR: PCIe 7.0? Understanding Why Now Is the Time to Transition

PCIe is familiar to legions of PC users as a high-performance enabler for expansion slots, especially GPU-based graphics cards and M.2 SSDs. It connects higher-bandwidth networking adapters and niche applications like system expansion chassis in server environments. Each PCIe specification generation has provided a leap… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?