TechInsights has been in the semiconductor analysis business for more than 35 years and is THE most trusted source of semiconductor information. TechInsights started as a reverse engineering and IP analysis company but has grown into much more. I remember waiting for the teardown reports before buying electronics to make sure… Read More

Intel Presents the Final Frontier of Transistor Architecture at IEDM

IEDM was buzzing with many presentations about the newest gate-all-around transistor. Both Intel and TSMC announced processes based on nanosheet technology. This significant process innovation allows the fabrication of silicon RibbonFET CMOS devices, which promise to open a new era of transistor scaling, keeping Moore’s… Read More

TSMC Unveils the World’s Most Advanced Logic Technology at IEDM

There was a lot of discussion at IEDM about the coming shift to gate-all-around (GAA) transistor structures. This new device brings many benefits to continue device scaling, both at the monolithic device level as well as for multi-die design. The path to GAA is not simple, there are new material, process and design considerations… Read More

An Invited Talk at IEDM: Intel’s Mr. Transistor Presents The Incredible Shrinking Transistor – Shattering Perceived Barriers and Forging Ahead

IEDM turned 70 last week. This was cause for much celebration in the form of special events. One such event was a special invited paper on Tuesday afternoon from Intel’s Tahir Ghani, or Mr. Transistor as he is known. Tahir has been driving innovation at Intel for a very long time. He is an eyewitness to the incredible impact of the Moore’s… Read More

IEDM Opens with a Big Picture Keynote from TSMC’s Yuh-Jier Mii

The main program for the 70th IEDM opened on Monday morning in San Francisco with an excellent keynote from Dr. Yuh-Jier Mii, Executive Vice President and Co-Chief Operating Officer at TSMC. Dr. Mii joined TSMC in 1994. Since then, he has contributed to the development and manufacturing of advanced CMOS technologies in both fab

PDF Solutions Hosts Executive Conference December 12 on AI’s Power to Transform Semiconductor Design and Manufacturing

PDF Solutions, Inc. will host an AI Executive Conference Thursday, December 12, in San Francisco featuring keynotes, presentations, panels and demonstrations offering insights into the power of AI to transform semiconductor design and manufacturing. The conference immediately follows the 70th Annual IEEE International… Read More

Is AI Intelligent? Insights from Ronjon Nag’s Presentation

In his keynote at the 2024 31st IEEE Electronic Design Process Symposium, Dr. Ronjon Nag, an adjunct professor at Stanford Medicine and president of the R42 Group, poses the provocative question: “Is AI Intelligent?” Drawing from four decades of pioneering work in AI, Nag blends personal anecdotes, scientific … Read More

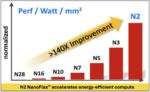

Silicon Creations is Fueling Next Generation Chips

Next generation semiconductor design puts new stress on traditionally low-key parts of the design process. One example is packaging, which used to be the clean-up spot at the end of the design. Thanks to chiplet-based design, package engineers are now rock stars. Analog design is another one of those disciplines.

Not long ago,… Read More

I will see you at the Substrate Vision Summit in Santa Clara

WIth packaging being one of the top sources of traffic on SemiWiki, I am expecting a big crowd at this event. A semiconductor substrate is a foundational material used in the fabrication of semiconductor devices. Substrates are a critical part of the manufacturing process and directly affect the performance, reliability, and… Read More

Alchip is Paving the Way to Future 3D Design Innovation

At the recent TSMC OIP Ecosystem Forum in Santa Clara, there was an important presentation that laid the groundwork for a great deal of future innovation. Alchip and its IP and EDA partner Synopsys presented Efficient 3D Chiplet Stacking Using TSMC SoIC. The concept of 3D, chiplet-based design certainly isn’t new. SemiWiki maintains… Read More

Semidynamics Unveils 3nm AI Inference Silicon and Full-Stack Systems