You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 826

[filter] => raw

[cat_ID] => 159

[category_count] => 826

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 159

[name] => Siemens EDA

[slug] => siemens-eda

[term_group] => 0

[term_taxonomy_id] => 159

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 826

[filter] => raw

[cat_ID] => 159

[category_count] => 826

[category_description] =>

[cat_name] => Siemens EDA

[category_nicename] => siemens-eda

[category_parent] => 157

[is_post] =>

)

Bruce Caryl is a Product Specialist with Siemens EDA

The most common way to evaluate a power distribution network is to look at its impedance over the effective frequency range. A lower impedance will produce less noise when transient current is demanded by the IC output buffers. However, this transient current needs to be provided… Read More

AI is the centerpiece of DAC this year. How to design chips to bring AI algorithms to life, how to prevent AI from hacking those chips, and of course how to use AI to design AI chips. In this latter category, there were many presentations, product announcements and demonstrations. I was impressed by many of them. But an important observation… Read More

Dan is joined by Dr. John Ferguson, Director of Product Management for the Calibre nmDRC and 3DIC related products for Siemens EDA. John has worked extensively in the area of physical design verification. Holding several patents, he is also a frequent author in the physical design and verification domain. Current activities … Read More

I wrote recently about a Siemens pre-announcement at DVCon on their directions in simulation+AI. On May 13th they officially announced a full spectrum of capabilities under the brand Questa One. Abhi Kolpekwar (VP/GM at Siemens EDA) more fully fleshed out the story for me. I asked why Siemens is late to this simulation+AI party.… Read More

In a keynote delivered at this year’s Siemens EDA User2User event, CEO Mike Ellow presented a focused vision for the evolving role of electronic design automation (EDA) within the broader context of global technology shifts. The session covered Siemens EDA’s current trajectory, market strategy, and the changing landscape … Read More

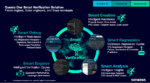

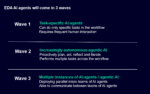

Author: Niranjan Sitapure, AI Product Manager, Siemens EDA

We are at a pivotal point in Electronic Design Automation (EDA), as the semiconductors and PCB systems that underpin critical technologies, such as AI, 5G, autonomous systems, and edge computing, grow increasingly complex. The traditional EDA workflow, which includes… Read More

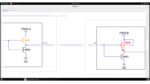

In the realm of mixed signal design for integrated circuits (ICs), level shifters play a critical role for interfacing circuits that operate at different voltage levels. A level shifter converts signal from one voltage level to another, ensuring compatibility between components. Figure 1 illustrates a missing level shifter… Read More

As semiconductor technology scales and device complexity increases, accurately modeling the parasitic effects of metal fill has become critical for circuit performance, power integrity, and reliability. Metal fill is a crucial part of the manufacturing process, ensuring uniform layer density, improving planarization,… Read More

We all know semiconductor design is getting harder. Much harder when you consider the demands of AI workloads and heterogeneous integration of many chiplets in a single package. This class of system demands co-optimization across the entire design flow. For example, functional verification, thermal analysis, signal and power… Read More

IC designs need to operate reliably under varying conditions and avoid inefficiencies like leakage across power domains. But how do you verify that connections between IP blocks has been done properly? This is where reliability verification, Electrical Rule Checking (ERC) tools and dynamic simulations all come into play particularly… Read More