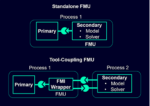

Co-simulation, two or more simulations running concurrently in some manner, is not a new idea. I have written before about multiphysics systems able to model thermal, stress, CFD and other factors simultaneously. I just read a white paper from Siemens based on a different method, using an open standard called the Functional Mockup… Read More

Siemens U2U 3D IC Design and Verification Panel

Given the success of the event in Silicon Valley last week, I would expect the Siemens U2U event in Munich to be even bigger. In my experience this has been the best user driven event in 2026 with the deepest customer content. EDA has always been a customer driven industry and it is good to see us recognize that from time to time. Kalar … Read More

Solving the EDA tool fragmentation crisis

By Samar Abd El-Hady and Wael ElManhawy

Design teams today face an uncomfortable truth: the specialized tools they need to verify modern ICs can’t reliably share the same design data. As geometries shrink below five nanometers and designs incorporate billions of transistors across multiple dies, no single Electronic… Read More

Complex PCB signoff challenges

Many complex PCB designs have high data-rate signals like USB, PCIe, DDR and HDMI which call for more thorough verification methods to ensure compliance plus mitigate any signal integrity, power integrity and EMI/EMC issues. Siemens has a methodology that uses automated rule-based electrical verification with an EDA tool,… Read More

WEBINAR: Beyond Moore’s Law and The Future of Semiconductor Manufacturing Intelligence

This is a live panel with industry experts who are on the leading edge of AI in semiconductor manufacturing. This is a must attend event for all levels of semiconductor professionals. I hope to see you there.

The semiconductor industry faces unprecedented challenges as it pushes toward advanced nodes below 3nm, managing exponential… Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White Paper

Review the specifications of any state-of-the-art microcontroller and you will discover the high dynamic current the device can consume. Examining the high clock rates and low tolerable voltage drop will lead you to the all-important power delivery network, or PDN. Components here include power planes, layer stack-up, decoupling… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design Enablement

The recent Chiplet Summit in Santa Clara was buzzing with new designs and new design methods. It felt like the industry had turned a corner at this year’s event with lots of new technology and design success on display. Siemens EDA had a large presence at the show and took home the Best in Show Award for Packaging Design. There were a … Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB Design

Though terminology sometimes get fuzzy, consensus holds that an agent manages a bounded task with control through a natural language interface. An agentic orchestrator, itself an agent, manages a more complex objective requiring reasoning through multi-step actions and is responsible for orchestrating those actions. By… Read More

Accelerating Computational Lithography Using Massively Parallel GPU Rasterizer

As semiconductor manufacturing pushes deeper into the nanometer regime, computational lithography has evolved from a supporting step into a central pillar of advanced chip design. Mask synthesis, lithography simulation, and optical proximity correction (OPC) now demand unprecedented levels of accuracy and computational… Read More

Formal Verification Best Practices

How do I know when my hardware design is correct and meets all of the specifications? For many years the answer was simple, simulate as much as you can in the time allowed in the schedule and then hope for the best when silicon arrives for testing. There is a complementary method for ensuring that hardware design meets the specifications… Read More