Traditional RF board design strategies based on circuit simulation worked at lower frequencies and relatively large spacing between components. Higher frequencies and densification dominate RF designs now, where corresponding wider bandwidths and tighter layouts with closely spaced components produce more complex 3D… Read More

Author: Don Dingee

Webinar: RF design success hinges on enhanced models and accurate simulation

Crosstalk, 2kAmp power delivery, PAM4, and LPDDR5 analysis at DesignCon

High-speed digital (HSD) designers have long tested the limits of realizable speed. GHz frequencies are now the norm, and multi-level signaling is pushing rates higher while the long-awaited transition to optical signaling and even higher rates looms ever closer. Power density is also climbing, and data-hungry applications… Read More

Chiplet integration solutions from Keysight at Chiplet Summit

Chiplets continue gaining momentum, fueled in large part by applications for AI and 5G/6G RFICs. Keysight has a strong presence at this year’s Chiplet Summit in Santa Clara, which includes Simon Rance in a super panel discussing “Chiplets: The Key to Solving the AI Energy Gap” and Nilesh Kamdar with a keynote… Read More

AI PC momentum building with business adoption anticipated

And just like that, the AI PC arrived. It will be hard to miss high-profile advertising campaigns like the one just launched by Microsoft touting them. Gartner said this September that AI PCs will be 43% of all PC shipments in 2025 (with 114M units projected) and that by 2026, AI PCs will be the only choice for business laptop users. … Read More

Ultra Ethernet and UALink IP solutions scale AI clusters

AI infrastructure requirements are booming. Larger AI models carry hefty training loads and inference latency requirements, driving an urgent need to scale AI acceleration clusters in data centers. Advanced GPUs and NPUs offer solutions for the computational load. However, insufficient bandwidth or latency between servers… Read More

Certification for Post-Quantum Cryptography gaining momentum

A crucial step in helping any new technology specification gain adoption is certification. NIST has been hard at work establishing more than post-quantum cryptography algorithms – they’ve also integrated the new algorithms into their process for third-party validation testing to ensure implementations are as advertised.… Read More

GaN HEMT modeling with ANN parameters targets extensibility

Designers choosing gallium nitride (GaN) transistors may face a surprising challenge when putting the devices in their context. While the Advanced SPICE Model for GaN HEMTs (ASM-HEMT) model captures many behaviors like thermal and trapping effects, it grapples with accuracy over a wide range of bias conditions. Foundries … Read More

Keysight EDA 2025 launches AI-enhanced design workflows

The upcoming Keysight EDA 2025 launch has three familiar tracks: RF circuit design, high-speed digital circuit design, and device modeling and characterization. However, this update features a common thread between the tracks – AI-enhanced design workflows. AI speeds modeling and simulation, opening co-optimization for… Read More

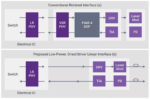

MIPI solutions for driving dual-display foldable devices

Flexible LCD technology has spurred a wave of creativity in device design, including a new class of foldable phones and an update to the venerable flip phone. Besides the primary display inside the fold – sometimes taking the entire inside area – a smaller secondary display is often found outside the fold. Introducing the secondary… Read More

Linear pluggable optics target data center energy savings

Data center density continues growing, driving interconnect technology to meet new challenges. Two of the largest are signal integrity and power consumption. Optical interconnects can solve many signal integrity issues posed by copper cabling and offer support for higher frequencies and bandwidths. Still, through sheer… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center