SYSTEM

CppSim – system-level simulator by creating C++ code of your schematic

PandA-bambu – framework for research in high-level synthesis and HW/SW co-design

QElectroTech – Electronic diagrams

SystemC – system design and modeling

SVALint – Linter for SystemVerilog Assertions (SVA)

Switchboard – framework for communication between distinct hardware models, such as RTL simulations, RTL on FPGAs and fast SW models.

WaveDrom – draws your Timing Diagram or Waveform from simple textual description

PCB

Electric – IC design with schematic capture, layout, routing, LVS, PCB layout

eSim – Circuit design, simulation, analysis, PCB design using KiCad, Ngspice, Verilator, Makerchip, GHDL and OpenModelica.

Fritzing – Schematic capture and PCB layout

gEDA – Schematic capture

gerber2ems – openEMS simulation based on Gerber files

Horizon EDA – Schematic and PCB layout

Icestudio – Visual editor for open FPGA boards.

KiCAD – PCB layout

KiCanvas – interactive, browser-based viewer for KiCAD schematics

KTechLab – Electronic and PIC microcontroller design

LibrePCB – PCB Layout

LTspice – SPICE simulation, schematic capture, waveform viewer, Analog Devices

openEMS – electromagnetic field solver using the FDTD method.

PCB – PCB layout

pcb-rnd – PCB layout

QSPICE – simulator, schematic capture and waveform viewer for RF and power circuits, free from Qorvo

IC

ASG – An automatic schematic generation tool from a SPICE netlist, usually of output from qflow.

ALIGN – Analog IC layout synthesis

Alliance/Coriolis – VHDL compiler, simulator, logic synthesizer, automatic place and route

Amaranth – Python-based HDL toolchain

Animate – Virtuoso schematic users can quickly see an automated analog layout, freemium tool from Pulsic

CflexHDL – design digital circuits in C, simulate really fast with a regular compiler.

ChipVault – Verilog and VHDL hierarchy management tool

Chisel – Hardware compiler framework

cocotb – coroutine based co-simulation testbench environment for verifying

Covered – Verilog code coverage

VHDL and SystemVerilog using Python

CUGR – Global routing tool developed by CUHK

CVC – Circuit Validity Checker, for errors in CDL netlist.

DEVSIM TCAD – semiconductor device simulator

EDA Playground – free web application for HDL simulation and synthesis

Edalize – Python library for interfacing EDA tools (Icarus, Yosys, ModelSim, Vivado, Verilator, GHDL, Quartus)

Fault – Design for Test

FuseSoc – package manager and a set of build tools for HDL code.

Gaw – Gtk Analog Wave viewer

GDSfactory – Python library for GDS generation

GDSpy – Python module for creation and manipulation of GDS files

GEM – RTL logic simulator with CUDA acceleration

GHDL – G HDL, a VHDL analyzer, compiler, simulator and synthesizer

Glade – Gds, Lef And Def Editor – layout and schematic editor, DRC, extraction, LVS.

Gnucap – GNU Circuit Analysis Package

GtkWave – waveform plot tool for digital simulation

Icarus Verilog – Verilog simulator (free)

iEDA – EDA infrastructure and tools from netlist to GDS for ASIC design

IIC-OSIC-TOOLS – Docker container of open-source IC tools

ipyxact – Python based IP-XACT parser

IRSIM – switch-level simulator

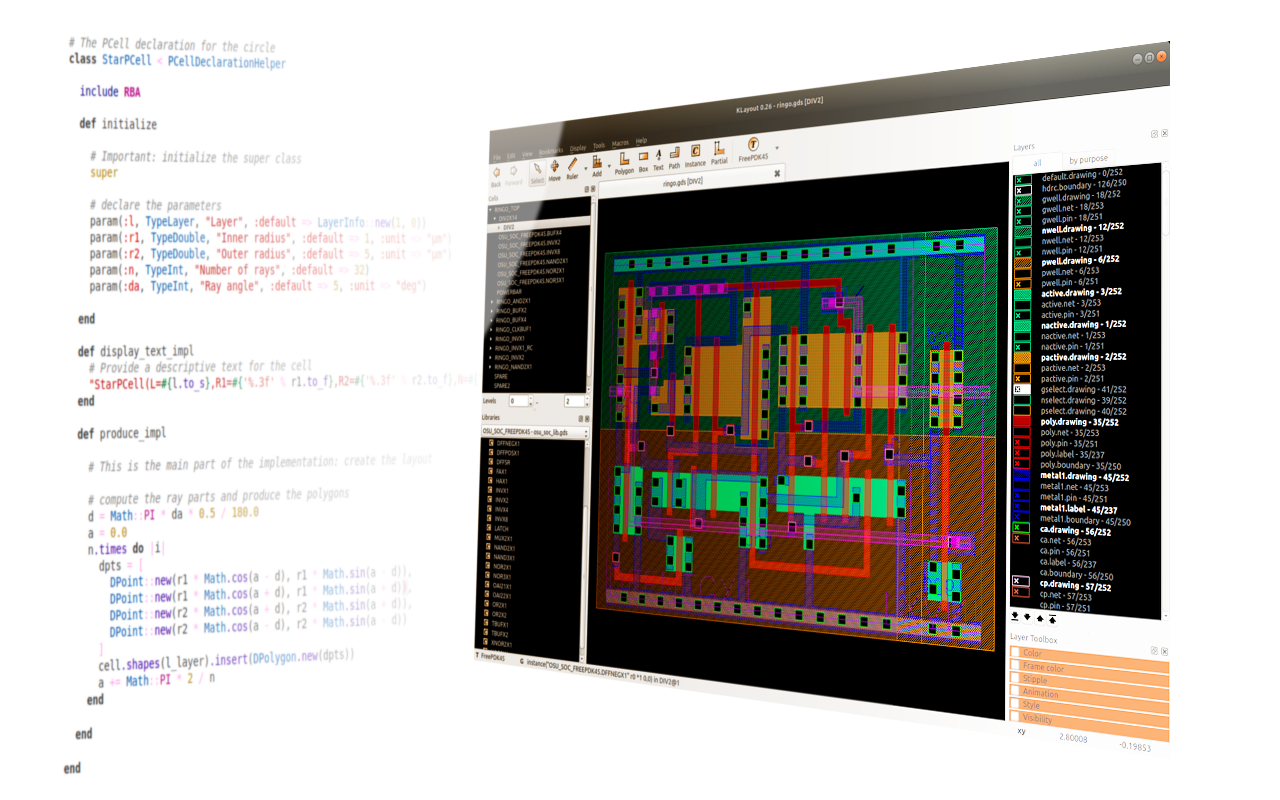

KLayout – Mask layout tool

LibrEDA – place and route

Linty HDL Designer – free linter for VHDL, Verilog, SystemVerilog, Tcl

LiteX – Migen/MiSoC based Core/SoC builder

Magic – IC layout, extraction, DRC

Makerchip-app – Desktop connection to free online Makerchip IDE

Migen – Python toolbox for HDL design

Mosaic – schematic capture and simulation tools

MyHDL – Python as a hardware description and verification language

Netgen – Layout Versus Schematic (LVS) tool

NetlistSVG – draws SVG netlist from Yosys JSON netlist

nMigen – Python based HDL design

Ngspice – SPICE circuit simulation

NVC – VHDL simulator and compiler

Open_PDKs – PDK setup scripts

OpenLane – digital RTL2GDS flow

Open Logic – a VHDL standard library for FPGA designs

OpenRAM – Memory compiler development framework

OpenROAD – RTL to GDS in 24 hours, no human in the loop

OpenSTA – Static Timing Analyzer

OpenTimer – Static Timing Analysis tool

OpenVAF – Verilog-A compiler

ORDeC – custom IC design platform

Oregano – schematic capture and SPICE circuit simulation

OSVVM – A VHDL verification framework, utility library, verification component library, and a simulator independent scripting flow

Padring – padring generation tool

PeakRDL – control and status register (CSR) toolchain.

PipelineC – HLS using C

PyCell Studio – create PyCells with Python and OpenAccess

PyRTL – collection of classes for Pythonic RTL design

PySlint – Python based SystemVerilog linter for testbenches, UVM, DPI and SVA.

PySpice – interface Ngspice and Xyce from Python

PyVerilog – Python toolkit for Verilog

Qrouter – multi-level, over-the-cell maze router

Qucs – Quite Universal Circuit Simulator

RePlAce – global placement tool

Revolution EDA – Symbol and schematic editor, layout editor, integration with Xyce for circuit simulation

RgGen – code generation tool for configuration and status registers

Risc-v toolchain – GNU compiler toolchain for RISC-V RV32! cores

SandPiper-SaaS – CLI connection to free (though proprietary) SandPiper™ microservice for TL-Verilog compilation.

SiliconCompiler – modular build system for hardware

sky130 – SkyWater Technologies 130nm CMOS PDK

slang – SystemVerilog language services

SPEF-Extractor – A Python library that reads LEF and DEF files, extract RC parasitics then create a SPEF file

SpiceGenTcl – control Spice simulators (Ngspice, Xyce) using Tcl

SpinalHDL – HDL that creates VHDL or Verilog

Spyci – analyze or plot ngspice or xyce output data with Python

Surfer – an extensible and snappy waveform viewer

SystemRDL – generic compiler front-end for Accellera’s SystemRDL 2.0 Register Description Language.

Tbengy – Python tool for SV/UVM testbench generation and RTL synthesis, uses Vivado and Digilent FPGA boards

TerosHDL – code verification for ASIC/FPGA designs

v2k-top – Verilog-AMS parser/simulation framework

Verilator – Verilog simulator

Vlog2Verilog – Verilog file conversion

VLSIFFRA – Create fast and efficient standard cell based a

VUnit – an open source unit testing framework for VHDL/SystemVerilog.

WRspice – Circuit simulator.

XCircuit – Schematic capture for SPICE netlists and PostScript

Xschem – Schematic capture and netlisting: VHDL, Verilog, SPICE.

Xic – Schematic capture and IC layout editor.

XLS – XLS implements a High Level Synthesis (HLS) toolchain which produces synthesizable designs (Verilog and SystemVerilog) from flexible, high-level descriptions of functionality.

Xyce – Parallel analog circuit simulator from Sandia National Laboratories

Yosys – Verilog RTL synthesis

yosys-slang – SystemVerilog frontend for Yosys

FPGA

CflexHDL – Design digital circuits in C, simulate really fast with a regular compiler. Flow from C -> Silice -> Verilog -> Migen/LiteX -> Bitstream

FOEDAG – Framework Open EDA Gui

fpga-bitstream – Generate a generica or fabric dependent bitstream

Logik – FPGA toolchain that fully automates converting RTL to bits, including synthesis, placement, routing, bitstream generation, and analysis

nextpnr – FPGA place and route

OpenFPGA – framework that enables rapid prototyping of customizable FPGA architectures

openFPGALoader – universal utility for programming FPGAs

Project IceStorm – Lattice bitstream format documentation

Qflow – digital synthesis flow using Verilog or VHDL, targets Xilinx or Altera

Raptor – commercial FPGA flow for FPGA design, RapidSilicon

SymbiFlow – FPGA framework for tools, Verilog to bitstream

Things From Intel 10K That Make You Go …. Hmmmm