IC designers are tasked with meeting specifications like robustness in SRAM bit cells where the probability of a violation are lower than 1 part-per-billion (1 ppb). Another example of robustness is a Flip-Flop register that must have a probability of specification violation lower than 1 part-per-million (1 ppm). Using Monte… Read More

Tag: verify high-sigma design

Moore’s Law and 28nm Yield

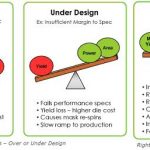

This blog is a follow-up to my second most viewed page Moore’s Law and 40nm Yield, with a strong recommendation of how to design for yield at the advanced nodes (32/28/22nm) with Verify High-Sigma design technology.

Case in point: Circuit blocks such as complex standard cells or memory bit cells are repeated thousands or even millions… Read More