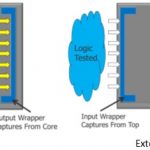

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

Tag: testkompress

Taming The Challenges of SoC Testability

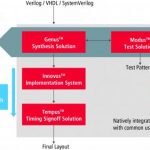

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More

Highest Test Quality in Shortest Time – It’s Possible!

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

A Most Significant Man

Most of us live perfectly good lives without distinction, fame, or note. Others rack up the honors, filling their walls and resumes with recognition of their brilliance. Like Dr. Janusz Rajski.

Rajski is the director of engineering for the test products at Mentor Graphics, an IEEE Fellow, and the inventor of embedded deterministic… Read More