Formal verification has made significant inroads in RTL and gate-level verification because it provides complementary strengths to conventional dynamic verification methods; using both provides higher levels of coverage and confidence in the correctness of an implementation. I haven’t heard as much about formal use in … Read More

Tag: sequential equivalence

Checking Clock Gating Equivalence the Easy Way

Synopsys just delivered a Webinar on using the sequential equivalence app (SEQ) in their VC Formal product to check that clock-gating didn’t mess up the functional intent of your RTL. This webinar is one in a series on VC Formal, designed to highlight the wide range of capabilities Synopsys has to offer in formal verification. They… Read More

Webinar: Synopsys on Clock Gating Verification with VC Formal

Clock gating is arguably the mostly widely-used design method to reduce power since it is broadly applicable even when more sophisticated methods like power islands are ruled out. But this style can be fraught with hazards even for careful designers. When you start with a proven-correct logic design and add clock gating, the logic… Read More

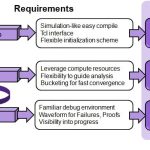

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More