In our previous article bearing the same title, we discussed the recommended baseline checks covering cell and pin presence, back-end, and some front-end checks related to functional equivalency. In this article, we’ll cover the extensive list of characterization checks, that include timing arcs, NLDM, CCS, ECSM/EM, and … Read More

Tag: pocv

We Need Libraries – Lots of Libraries

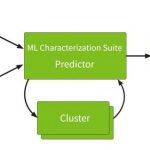

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Machine Learning Accelerates Library Characterization by 50 Percent!

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

Variation Alphabet Soup

On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More