A growing trend in system design is the use of multiple ICs mounted in advanced packages, especially in high-performance computing and AI. These modern packages now integrate multiple ICs, often with high-bandwidth memory (HBM), resulting in hundreds of thousands of connections that need proper verification. Traditional… Read More

Tag: lvs

Addressing Reliability and Safety of Power Modules for Electric Vehicles

As electric vehicles (EVs) gain widespread adoption, safety, reliability, and efficiency are becoming increasingly important. A crucial component in ensuring these aspects is the power module (PM), which manages the energy flow between the EV battery and the motor. The design of these power modules must not only meet the high-performance… Read More

Maximizing 3DIC Design Productivity with 3DBlox: A Look at TSMC’s Progress and Innovations in 2024

At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

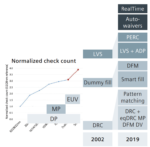

Smarter, Faster LVS using Calibre nmLVS Recon

Back in the 1970s we did Layout Versus Schematic (LVS) checks manually, so when internal EDA tools arrived in the 1980s it was a huge time saver to use LVS in finding the differences between layout and schematics. One premise before running LVS is that both layout and schematics are complete and ready for comparisons. Fast forward… Read More

Soft checks are needed during Electrical Rule Checking of IC layouts

IC designs have physical verification applications like Layout Versus Schematic (LVS) at the transistor-level to ensure that layout and schematics are equivalent, in addition there’s an Electrical Rules Check (ERC) for connections to well regions called a soft check. The connections to all the devices needs to have the most… Read More

Successful 3DIC design requires an integrated approach

While the leap from traditional SoC/IC designs to Three-Dimensional Integrated Circuits (3DICs) designs brings new benefits and opportunities, it also introduces new challenges. The benefits include performance, power efficiency, footprint reduction and cost savings. The challenges span design, verification, thermal… Read More

Ensuring 3D IC Semiconductor Reliability: Challenges and Solutions for Successful Integration

One of the most promising advancements in the semiconductor field is the development of 3D Integrated Circuits (3D ICs). 3D ICs enable companies to partition semiconductor designs and seamlessly integrate silicon Intellectual Property (IP) at the most suitable process nodes and processes. This strategic partitioning yields… Read More

3D IC – Managing the System-level Netlist

I just did a Google search for “3D IC”, and was stunned to see it return a whopping 476,000 results. This topic is trending, because more companies are using advanced IC packaging to meet their requirements, and yet the engineers doing the 3D IC design have new challenges to overcome. One of those challenges is creating… Read More

Unlock first-time-right complex photonic integrated circuits

The capacity and energy efficiency challenges from the growing appetite for high-speed data along with advanced applications such as LIDAR and quantum computing are driving demand for increasingly large-scale photonic integrated circuits (PIC). With an ever-increasing number of components on a single photonic chip, manual… Read More

EDA in the Cloud – Now More Than Ever

A decade ago, many of us heard commentaries on how entrepreneurs were turned down by venture capitalists for not including a cloud strategy in their business plan, no matter what the core business was. Humorous punchlines such as, “It’s cloudy without any clouds” and “Add some cloud to your strategy and your future will be bright… Read More