When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

Tag: low voltage

Ultra-low Voltage: Is Your Slack Really Positive? Are You Sure?

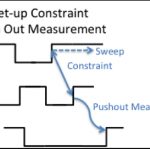

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

Voltage Limbo Dancing: How Low Can You Go?

All chips these days have to worry about power. Indeed it is typically the top of the priority list of concerns, above performance and even area. Transistors are effectively fast and free, but you can’t have too many of them (at least turned on at once). The most obvious way to reduce power is to lower the supply voltage. This … Read More