In the relentless pursuit of ever-increasing data speeds, the 1.6 Terabits per second (Tbps) era looms on the horizon, promising unprecedented levels of connectivity and bandwidth within data centers. As data-intensive applications proliferate and the demand for real-time processing escalates, the need for robust and efficient… Read More

Tag: fec

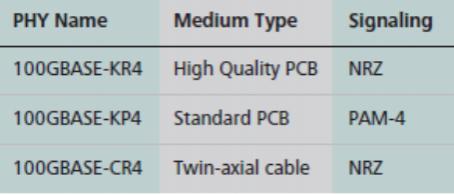

Unleashing the 1.6T Ecosystem: Alphawave Semi’s 200G Interconnect Technologies for Powering AI Data Infrastructure

In the rapidly evolving landscape of artificial intelligence (AI) and data-intensive applications, the demand for high-performance interconnect technologies has never been more critical. Even the 100G Interconnect is already not fast enough for infrastructure applications. AI applications, with their massive datasets… Read More

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

Alphawave IP is Enabling 224Gbps Serial Links with DSP

Alphawave IP is a new member of the SemiWiki community. You can learn about the company and their CEO, Tony Pialis in this interview by Dan Nenni. Design & Reuse did a virtual IP-SOC Conference recently and Tony presented. The D&R event had a very strong lineup of presenters. They supplemented the prepared video presentations… Read More

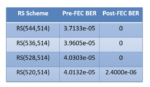

Multi-Channel Multi Rate FEC Engine Webinar with Open Silicon

I will be pleased to moderate on December 7[SUP]th[/SUP] the Open-Silicon webinar addressing the benefits of the multi-channel multi-rate forward error correction (MCMR FEC) IP and the role it plays in high-bandwidth networking applications, especially those where the bit error rate is very high, such as high speed SerDes … Read More

Webinar: Achieving Very High Bandwidth Chip-to-Chip Communication with the Interlaken Interface Protocol

Open Silicon will hold this webinar on June 13th at 8 am PDT (or 5 pm CE) to describe their Interlaken IP core, and how to achieve very high bandwidth C2C communication in various networking applications. To be more specific, the Interlaken protocol can be used to support Packet Processing/NPU, Traffic Management, Switch Fabric,… Read More