Berkeley Design Automation today announced the first silicon-accurate circuit simulation for mega-scale arrays like memories and CMOS image sensors. If this tool lives up to its claims, it is going to be a big deal for FinFET-based circuits, Memory designers are rightly worried about having the accuracy necessary to include… Read More

Tag: fastspice

Improving Design Practices for an Image Sensor IDM

With nearly twenty five years in business, Tanner EDA Application Engineers have seen a wide range of support requests. One consistent topic area is around design data management and design reuse. In one recent instance, our customer, an IDM who produces imaging sensors for infrared vision systems, called on Tanners AE team for… Read More

Hot Topic – CMOS Image Sensor Verification!

Mobile applications require CMOS image sensor devices that have a low signal-to-noise ratio (SNR), low power, small area, high resolution, high dynamic range, and high frame rate. CMOS image sensor imaging performance is noise limited requiring accurate noise analysis on the pixel array electronics and column readout circuitry.… Read More

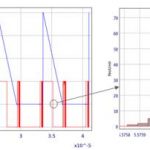

Transient Noise Analysis (TNA)

Tanner EDA Applications Engineers see a broad range of technical challenges that our users are trying to overcome. Here’s one worth sharing – it deals with transient noise analysis (TNA) for a comparator design. The customer is a producer of advanced flow measurement devices for application in medicine and research. The designer… Read More

Static Timing Analysis for Memory Characterization

Modern SoC (System On Chip) designs contain a larger number of RAM (Random Access Memory) instances, so how do you know what the speed, timing and power are for any instance? There are a couple of approaches:

[LIST=1]

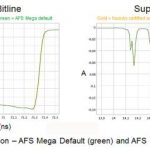

Analog FastSPICE update at DAC

Paul Estrada, COO of Berkeley DA met with me on the final day of DAC to provide an update. BDA coined the phrase Analog FastSPICE and have continued to dominate that market segment in the world of SPICE circuit simulators.… Read More

AMS Verification: Speed versus Accuracy

I spent Thursday Sept. 22 at the first nanometer Circuit Verification Forum, held at TechMart in Santa Clara. Hosted by Berkeley Design Automation (BDA), the forum was attended by 100+ people, with circuit designers dominating. I spoke with many attendees. They were seeking solutions to the hugely challenging problems they … Read More

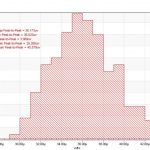

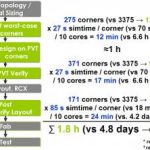

PVT and Statistical Design in Nanometer Process Geometries

On Sept 22, 2011, the nm Circuit Verification Forumwill be held in Silicon Valley, hosted by Berkeley Design Automation. At this forum, Trent McConaghy of Solido DA will present a case study on the TSMC Reference Flow 2.0 VCO circuit, to showcase Fast PVT in the steps of extracting PVT corners, verifying PVT, and doing post-layout… Read More