In the earliest days of IC design the engineering work was always done at the transistor-level, and then over time the abstraction level moved upward to gate-level, cell-level, RTL level, IP reuse, and high-level modeling abstractions. The higher levels of abstraction have allowed systems to be integrated into an SoC that can… Read More

Tag: diagnosis

Mentor Seminar: Evolution of diagnosis-driven yield analysis

It’s a fact that new process nodes come with some amount of yield challenges. One way to find and eliminate silicon defects is through diagnosis-driven yield analysis (DDYA), which is the topic of a free seminar by Mentor Graphics in Fremont this Thursday, October 10 from 11:30am – 2pm (yes, lunch is included because Mentor… Read More

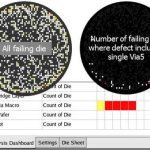

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More

Yield Analysis and Diagnosis Webinar

Sign up for a free webinar on December 11 on Accelerating Yield and Failure Analysis with Diagnosis.

The one hour presentation will be delivered via webcast by Geir Eide, Mentor’s foremost expert in yield learning. He will cover scan diagnosis, a software-based technique, that effectively identifies defects in digital logic… Read More