High-speed signals enable electronic systems by using memory interfaces, SerDes channels, data center backplanes and connectivity in automobiles. Challenges arise from signal distortions like inter-symbol interference, channel loss and dispersion effects. Multi-gigabit data transfer rates in High-Bandwidth Memory… Read More

Tag: dfe

How Channel Operating Margin (COM) Came to be and Why It Endures

According to a recent whitepaper by Samtec, Channel Operating Margin (COM) didn’t start as an algorithm; it started as a truce. In the late 2000s and early 2010s, interconnect designers and SerDes architects were speaking past each other. The former optimized insertion loss, return loss, and crosstalk against frequency-domain… Read More

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

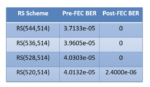

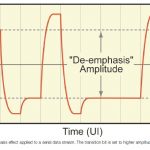

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

Navigating Memory Choices for Your Next Low-Power Design

Choosing a memory architecture can be a daunting task. There are many options to choose from, each with their own power, performance, area and cost profile. The right choice can make a new design competitive and popular in the market. The wrong choice can doom the whole project to failure.

Vadhiraj Sankaranarayanan, senior technical… Read More

Channel Operating Margin (COM) — A Standard for SI Analysis

There’s an old adage, attributed to renowned computer scientist Andrew Tannenbaum, one that perhaps only engineers find amusing: “The nice thing about standards is that you have so many to choose from.” Nevertheless, IEEE standards arise from customer requirements in the electronics industry. Many relate… Read More

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More