A week ago I was reading an article written by Daniel Nenni where he emphasised about semiconductor acquisitions to fuel innovation. We would see that in a larger space, not only in semiconductor and FPGA manufacturing companies (e.g. Intel and Altera) but also in the whole semiconductor ecosystem. If we see it from technical perspective,… Read More

Tag: bugscope

A Comprehensive Automated Assertion Based Verification

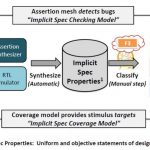

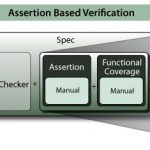

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

Assertion Synthesis: From Startup to Mainstream

In college many of us dreamed of starting up our own company by offering something new that has never been done before. Today I spoke by phone with Yunshan Zhuin Shanghai, and he has actually lived out this scenario by founding NextOp in 2006, then getting that company acquired by Atrentain 2012. The new capability that NextOp created… Read More

Making IP Reuse and SoC Integration Easier

The last graphics chip that I worked on at Intel was functionally simulated with only a tiny display size of 16×16 pixels, because that size allowed a complete regression test to be simulated overnight. Our team designed three major IP blocks: Display Processor, Graphics Processor and Bus Interface Unit. We wanted to also… Read More

A Methodology for Assertion Reuse in SoC Designs

As your SoC design can contain hundreds of IP blocks, how do you verify that all of the IP blocks will still work together correctly once assembled? Well, you could run lots of functional verification at the full-chip level and hope for the best in terms of code coverage and expected behavior. You could buy an expensive emulator to … Read More

Atrenta Japan Technoloogy Forum

As they have done for the last few years, Atrenta held its fifth annual user group meeting at the Shin Yokohama Kokusai Hotel on September 13. The attendees are a mixture of customers and other interested members of the semiconductor supply chain. There were nearly 90 people there representing 48 different companies in Japan.

The… Read More

Assertion Synthesis: Atrenta, Cadence and AMD Tell All

Assertion Synthesis is a new tool for verification and design engineers that can be used with simulation or emulation. At DVCon Yuan Lu of Atrenta is presenting a tutorial on Atrenta’s BugScope along with John Henri Jr of Cadence explaining how it helps emulation and Baosheng Wang of AMD discussing their experiences of the… Read More

Assertion Synthesis

In June, Atrenta acquired NextOp, the leader in assertion synthesis. So what is it?

Depending on who you ask, verification is a huge fraction, 60-80%, of the cost of an SoC design, so obviously any technology that can reduce the cost of verification has a major impact on the overall cost and schedule of a design. At a high-level, verification… Read More