In the relentless pursuit of ever-increasing data speeds, the 1.6 Terabits per second (Tbps) era looms on the horizon, promising unprecedented levels of connectivity and bandwidth within data centers. As data-intensive applications proliferate and the demand for real-time processing escalates, the need for robust and efficient… Read More

Tag: bit error rate

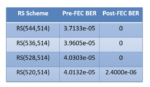

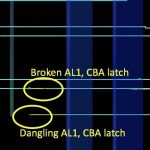

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

SRAM Optimization Saves Power on SOC’s and in Systems

Mobile device designers face the dilemma of reducing power and at the same time maintaining or increasing performance. Consumers will not tolerate increased battery life at the expense of performance. If it were otherwise, designers could simply dial back clock rates. Without this simple cure, the best way to reduce power for… Read More