The old adage that goes the one constant thing you can always count on is change, could easily be reworded for semiconductor design to say the one constant thing you can count on is variation. This is doubly true. Not only is variation, in all its forms, a constant factor in design, additionally the methods of analyzing and dealing … Read More

Tag: aocv

Crossfire Baseline Checks for Clean IP Part II

In our previous article bearing the same title, we discussed the recommended baseline checks covering cell and pin presence, back-end, and some front-end checks related to functional equivalency. In this article, we’ll cover the extensive list of characterization checks, that include timing arcs, NLDM, CCS, ECSM/EM, and … Read More

We Need Libraries – Lots of Libraries

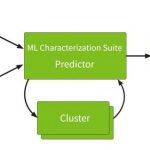

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Machine Learning Accelerates Library Characterization by 50 Percent!

Standard cell, memory, and I/O library characterization is a necessary, but time-consuming, resource intensive, and error-prone process. With the added complexity of advanced and low power manufacturing processes, fast and accurate statistical and non-statistical characterization is challenging, creating the need … Read More

Solutions for Variation Analysis at 16nm and Beyond

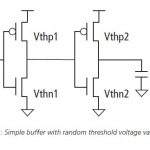

Variation is still the tough nut to crack for advanced process nodes. The familiar refrain of lower operating voltages and higher performance requirements make process variation an extremely important design consideration. As far back as the early 2000’s design teams have been looking for a better approach to model variation… Read More

A Better Way for Analog Designers to Perform Variation Analysis

The impact of process variation at advanced nodes is increasing — no surprise there. In recent years, the principal design emphasis to better reflect this variation has been the adoption of two new methodologies: (1) advanced on-chip variation (AOCV, as well as POCV/LVF) for digital static timing analysis, and (2) advanced… Read More

Variation Alphabet Soup

On-chip variation (OCV) is a major issue in timing signoff, especially at low voltages or in 20/16/14nm processes. For example, the graph below shows a 20nm inverter. At 0.6V the inverter has a delay of 2 (nominalized) units. But due to on-chip variation this might be as low as 1.5 units or as high as 3 units, which is a difference from… Read More

Signoff Accurate Timing Analysis at Improved Run-time & Capacity

The semiconductor design sizes, these days, can easily be of the order of several hundred millions of cells, adding into the complexity of verification. Amid ever growing design sizes, it’s a must that the timing verification is done accurately. Normally Static Timing Analysis (STA) is done to check whether all clocks and signals… Read More