Twenty eight nanometer is progressing very well. Our output and our yields are both above the plans that we set for ourselves and the plans that we communicated to our customers early in the year. Early in the year means January-February of the year, we set our plans in output and in yields and we, of course, ever since then we tried to… Read More

Tag: 28nm yield

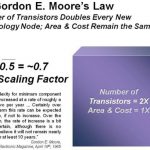

Moore’s Law and Semiconductor Design and Manufacturing

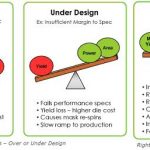

The semiconductor design and manufacturing challenges at 40nm and 28nm are a direct result ofMoore’s Law, the climbing transistor count and shrinking geometries. It’s a process AND design issue and the interaction is at the transistor level. Transistors may be shrinking, but atoms aren’t. So now it actually matters when even… Read More

Redefining the Foundry Model: TSMC versus GlobalFoundries

The 17[SUP]th[/SUP] annual TSMC Technical Symposium finished its North American tour in Boston, a day before the Boston Marathon. I would like to be clever and say the foundry business is also a marathon but it clearly is not. If you watch TSMC, the foundry business is both a sprint AND a marathon!

Moore’s Law and 28nm Yield

This blog is a follow-up to my second most viewed page Moore’s Law and 40nm Yield, with a strong recommendation of how to design for yield at the advanced nodes (32/28/22nm) with Verify High-Sigma design technology.

Case in point: Circuit blocks such as complex standard cells or memory bit cells are repeated thousands or even millions… Read More