Dave Hwang joined Alchip in 2021 as General Manager of Alchip’s North America Business Unit. He also serves as Senior Vice President, Business Development. Prior to join Alchip, Dave served as Vice President, Worldwide Sales and Marketing for Global Unichip and in a variety of management and technical roles at TSMC. He holds… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreSynopsys Expands Optical Interfaces at DesignCon

The exponential growth of cloud data centers is well-known. Driven by the demands of massive applications like generative AI, state-of-the-art data centers present substantial challenges in terms of power consumption. And AI is poised to drive a 160% increase in data center power demand while also increasing demands on storage… Read More

Trump whacking CHIPS Act? When you hold the checkbook, you make up the new rules

- News reports that Trump will change CHIPS Act to suit his views

- We specifically predicted this months ago as deals closed 11th hour

- Blue states, enemies list & foreign entities likely to get cut

- Big changes/cuts likely to a program Trump roundly criticized

Reuters: Exclusive: Trump prepares to change US CHIPS Act conditions,… Read More

AMAT- In line QTR – poor guide as China Chops hit home- China mkt share loss?

- QTR was just “in-line” but guide was below expectations

- We think its not just China export rules but share loss as well

- Leading edge is strong but obviously not enough to offset China

- Memory remains weak-Foundry (TSMC) is the primary driver

Headwinds slow growth to flat

Applied reported $7.166B in revenues and Non … Read More

Podcast EP274: How Axiomise Makes Formal Predictable and Normal with Dr. Ashish Darbari

Dan is joined by Dr. Ashish Darbari, CEO of Axiomise. Axiomise was founded in 2017 by Dr. Darbari, who has spent over two decades in the industry and top research labs increasing formal verification adoption. At Axiomise, they believe the only way to make formal methods mainstream for all semiconductor design verification is to… Read More

CEO Interview: Badru Agarwala of Rise Design Automation

Badru Agarwala is the CEO and Co-Founder of Rise Design Automation (RDA), an EDA startup with a mission to drive a fundamental shift-left in semiconductor design, verification, and implementation by raising abstraction beyond RTL With over 40 years of experience in EDA, Badru served as General Manager of the CSD division at… Read More

Webinar: Unlocking Next-Generation Performance for CNNs on RISC-V CPUs

The growing demand for high-performance AI applications continues to drive innovation in CPU architecture design. As machine learning workloads, particularly convolutional neural networks (CNNs), become more computationally intensive, architects face the challenge of delivering performance improvements while maintaining… Read More

An Open-Source Approach to Developing a RISC-V Chip with XiangShan and Mulan PSL v2

As RISC-V gains traction in the global semiconductor industry, developers are exploring fully open-source approaches to processor design. XiangShan, a high-performance RISC-V CPU project, combined with the Mulan Permissive License v2 (Mulan PSL v2), represents a community-driven, transparent alternative to proprietary… Read More

2025 Outlook Anna Fontanelli MZ Technologies

Anna Fontanelli, CEO of MZ Technologies, is a silicon executive with more than 35 years of expertise in managing complex R&D organizations/programs to give birth to innovative EDA technologies. Strong communication skills and proven ability to lead distributed, cross functional teams in international environments.… Read More

Embracing the Chiplet Journey: The Shift to Chiplet-Based Architectures

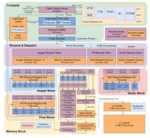

The semiconductor industry is facing a paradigm shift. Traditional scaling, once driven by Moore’s Law, is slowing down. For years, moving to smaller process nodes led to lower transistor costs and better performance. However, scaling from node to node now offers fewer benefits as wafer costs rise much more than the historical… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era