These were the closing words Yunsup Lee, CTO, SiFive used at one of the December RISC-V Summit Keynotes entitled ‘Opportunities and Challenges of Building Silicon in the Cloud’. Fired up was more the mood among the 1000+ attendees of the RISC-V Summit held at the Santa Clara Convention Center and SiFive was among the companies showcasing their latest offerings, providing an update among the increasingly active and productive ecosystem blending open-source initiatives with commercial products and services.[1]

Among the stats presented by Lee was the number of industry RISC-V cores released which will soon reach (in less than five years) more than 70 cores. 5,000+ registered to attend the SiFive Global City Tours and 500+ fabless semiconductor companies have contacted SiFive.

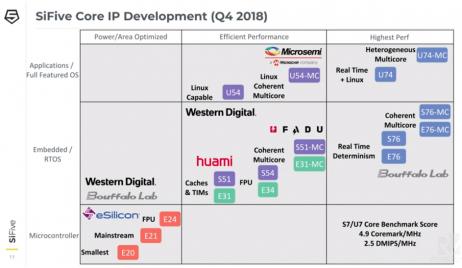

SiFive’s Core IP comprises the 2, 3, 5, and 7 Series. Each numbered series is a product family and comprises 32 and 64-bit offerings in E, S, and U variants. E cores are 32 bit embedded cores, S cores are 64-bit high performance embedded cores, and U cores are Linux-capable. Each Core IP Series comprises standard cores as well as cores that can be fully customized with the features of each available Core IP Series.

SiFive’s Core IP portfolio has rapidly expanded of late. In February 2018, the E2 cores of the 2 Series Core IP were launched. These are SiFive’s most efficient cores optimized for power and area. At the recent Linley conference, six cores were announced (E7, S7, U7, and their multicore versions) including the highest performance S76 and E76 cores with real-time determinism, the S76-MC, and E76-MC coherent multicores, the U74 real-time + Linux, and the U74-MC Heterogenous Multicore (used by Bouffalo Lab). The S7/U7 Core benchmarks clock at 4.9 Coremark/MHz and 2.5 DMIPS/MHz

Announced standard cores to date include the E20, E21, E24, E31, E34, S51, S54, U54, and U54-MC. Recent customizable Core IP design wins include eSilicon, Bouffalo Labs and Western Digital. The E31 has been implemented by Huami. SiFive also announced floating point features in numerous cores including the S54 and E34. The Linux-capable, coherent multicore U54-MC is used by Microsemi, a Microchip company while FADU has selected S51-MC and E31-MC coherent multicores with FPUs.

[1] The RISC-V Foundation Summit had about 1,200 registrations, with 32 countries and 23 states represented at the Summit, 29 exhibitors, 9 keynotes, 4 panels, 53 presentations, and 1 hackathon

The SiFive Embedded Software Ecosystem is growing, complementing SiFive Freedom Studio with offerings and compatible services from SEGGER, Lauterbach, IAR, Ashling, Imperas, UltraSOC with Embedded OSes like Express Logic-ThreadX, FreeRTOS, Zephyr, Micrium uCOS, RIOT, RTEMS, NuttX.

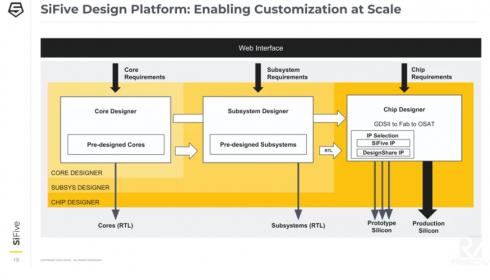

SiFive is building products to allow customization at scale with their online design platform with a web interface, allowing for the generation of customized RTL with their Core Designer. Eventually, Core Designer designs will be able to put into the Subsystem Designer to build RTL ready subsystems which can then be integrated with the Chip Designer (currently in development stage) to generate a chip for prototyping and silicon production readiness. Currently, only a web preview of the Chip Designer is available; an SoC template incorporates DesignShare IP from 3[SUP]rd[/SUP] part vendors (currently numbering 20), SiFive IP, and custom IP. All this is done through a cloud infrastructure (Microsoft Azure), in conjunction with an EDA tools company (Cadence) with SiFive offering the front-end Design Layer platform and managing the back-end Fab and OSAT packaging and test relationships. The proof of concept SoC was taped out in September (see below).

A variant of the FU540 was taped out in 28nm to prove the methodology. The variant was the first to utilize the combined cloud environment of TSMC’s VDE (Virtual Design Environment, announced at TSMC’s last OIP event), with Cadence tools, hosted on Microsoft Azure, with a SiFive’s web-based design integration and aggregation.

A variant of the FU540 was taped out in 28nm to prove the methodology. The variant was the first to utilize the combined cloud environment of TSMC’s VDE (Virtual Design Environment, announced at TSMC’s last OIP event), with Cadence tools, hosted on Microsoft Azure, with a SiFive’s web-based design integration and aggregation.

When asked what the biggest impediment to faster RISC-V adoption was, Yunsup Lee cited FUD (Fear, Uncertainty, Doubt) concerns and questions on whether the ecosystem is mature enough. He stressed that RISC-V is here and with everyone’s help working on RISC-V, it will be even stronger.

Yunsup Lee earlier had another presentation with Frans Sijstermans of NVIDIA where he described SiFive’s Freedom Unleashed Platform running NVIDIA’s open-source Deep Learning Accelerator (NVDLA) targeted toward edge devices and IoT. I had a chance to chat with him about this and he described a demo using a RISC-V Linux processor talking to NVDLA and running YOLO (You Only Look Once) v3 open source network. All components to test that out are open sourced and the code can be downloaded by anyone.

Summit announcements included Microsemi’s PolarFire SoC architecture which brings real-time deterministic asymmetric multiprocessing (AMP) capability to Linux platforms in a multi-core coherent central processing unit (CPU) cluster. This architecture, developed in collaboration with SiFive, features a flexible 2 MB L2 memory subsystem that can be configured as a cache, scratchpad or direct access memory. A PolarFire SoC development kit is also available, consisting of the PolarFire FPGA-enabled HiFive Unleashed Expansion Board and SiFive’s HiFive Unleashed Development Board with its RISC-V microprocessor subsystem and NVIDIA’s NVDLA was onboarded among a flurry of announcements.

Lee mentioned that SiFive’s strategy to build the HiFive Unleashed development board and getting the software stack going is helping the security aspects and all the software being ported is great to see and is helping the ecosystem. The next steps for SiFive are to increase adoption with some people who are still on the sidelines by highlighting the successes. For example, FADU in Korea announced that they used the S5 series as a real product reporting 1/3 of the area and 1/3 of the power required had they used standard cores. In addition, standard cores had features that they did not need. SiFive gave them a tailored implementation.

Software and hardware are important, and people want the easiest way to solve their problems. People are seeing the benefits of this approach since they cannot build only one chip due to the requirements being diverse. According to Lee, SiFive is building what customers want who are now asking for high- performance templates with HBM, Interlaken, high-speed Ethernet, high-speed SerDes. SiFive is getting a lot of pull on AI/ML and automotive safety requirements, edge compute, industrial solutions whose needs are not currently being satisfied. More custom solutions will be needed, and customers will see that standard products do not meet their needs and a customizable and configurable Design Platform will be the way to go. In summary, Yunsup Lee came to the Summit to deliver one message: RISC-V is here. RISC-V is safe. RISC-V is better. You will not get fired for choosing RISC-V.

[1] The RISC-V Foundation Summit had about 1,200 registrations, with 32 countries and 23 states represented at the Summit, 29 exhibitors, 9 keynotes, 4 panels, 53 presentations, and 1 hackathon

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.