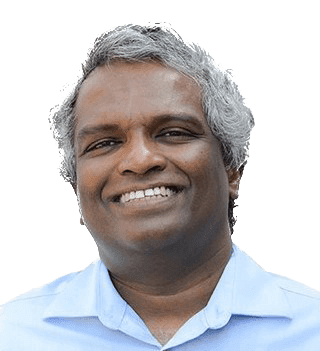

Rabin Sugumar was Distinguished Engineer and Chief Architect at Marvell/Cavium and built and led the architecture group for the ThunderX Arm server processor line. Most recently he led the architecture of the ThunderX3 processor, which had industry leading single thread performance and socket level performance at time of silicon.

Prior to Marvell/Cavium, he was at Broadcom where he was one of the lead architects on the server processor that became ThunderX2. ThunderX2 was the first Arm server to achieve single thread and socket level performance comparable to high end Intel Xeon servers and paved the way for Arm servers in the data center. During Rabin’s career, he has also worked on architecture and design of vector processors at Cray Research, early multi-threaded and out-of-order SPARC processors at Sun Microsystems, and InfiniBand adapters at Sun Microsystems/Oracle.

Rabin obtained his PhD in Computer Science and Engineering from the University of Michigan. The cache simulator he wrote during his PhD is still widely used in academia. Rabin has over 25 years of experience in CPU architecture and design, and 28 granted patents.

Tell us about your company?

Akeana was founded over 4 years ago and came out of stealth August 2024. We were formed with an engineering team that has been together for over 20 years, with a proven record of pioneer processor development. If you ever wondered where the Cavium/Marvell ThunderX2 processor team went to, well they are at Akeana now.

Akeana is a provider of RISC-V ISA based processors and subsystems IP. We offer a broad range of cores from ultra small 100-series, compute/data movement optimized 1000-series and ultra-high performance 5000 series. On top of core products, we offer interconnect fabrics (coherent and non-coherent), System IP blocks, and application specific hardware accelerators. We are unique in the RISC-V world of offering the same breadth of processors and interconnect IP as ARM.

What problems are you solving?

We solve the performance problem, which comes into two main categories. First, sheer performance and second, optimal performance per area/power. For sheer performance we offer industry leading performance RISC-V processors, as well as scaling to large multi-core systems. Optimum performance comes from efficient compute per area/power but also data movement optimizations and customizations. This is provided with highly efficient, customizable RISC-V cores and accelerators as well as optimized connectivity fabrics in multi-core systems.

Customers may further configure and customize the processors and systems to meet their compute and data PPA (performance, power and area) points.

What application areas are your strongest?

We thrive in a broad range of applications which require high performance and customized compute subsystems. For example, AI chips or chiplets used in Datacenter and Edge AI where compute, accelerator and interconnect fabrics need to be combined in different ways to optimize execution of relevant AI models. We also have seen great traction for Akeana in Automotive. We see the ‘Server on Wheels’ trend of automotive intersect very well with Akeana’s strengths. Physical AI is another area with our customers/partners. Our ability to configure a core for real-time, low latency compute sets us apart in this area. And the traditional high performance compute use cases in Datacenter and Mobile are becoming increasingly RISC-V friendly, and we play well in this area given our efficient performance and strong focus on compliance with standards.

What keeps your customers up at night?

Computation and algorithm needs are changing so quickly, especially with the usage of AI algorithms in a broad range of applications. Customers see their competitors constantly evolving and supporting newer AI models, use cases and fear losing ground in this evolving landscape. With Akeana customizable RISC-V cores and multi-core fabrics we can provide customers with the performance points they need for compute and data movement, as well as the flexibility to respond to market and algorithm changes. RISC-V is emerging as an AI native heterogeneous hardware-software co-design platform, and this is what Akeana is enabling for our AI chip customers.

Some other customers have other worries, that as their SoCs are battery powered, they are power sensitive. The(se) customers need software flexibility, high performance compute and data movement, but at lowest power possible. With our highly efficient compute and data movement systems, we enable customers to operate at very low power with the most efficiency. Other customers need customized AI solutions for their use cases, but so far have not had to build expertise in-house to architect and design the AI solutions they need. For such customers, Akeana functions as a design expert resource, helping them through architecture and performance decisions and providing design assistance to pull together AI subsystems.

What does the competitive landscape look like, and how do you differentiate?

The competitive landscape is changing with many recent acquisitions of RISC-V based solution providers. These acquisitions contribute to an increase in RISC-V adoption and validate the overall RISC-V approach to compute.

We differentiate on performance and the completeness of our IP solutions where we are able to pull together entire compute subsystems all developed and designed to work well together. We also have a strong design team that is able to work with customers to architect, design, and deliver fully validated subsystems.

What new features/technology are you working on?

We have just integrated Simultaneous Multi-threading (SMT) into our cores, as an option if the customer desires the latency hiding and concurrency enabled by SMT. We exhibited this functionality in multiple demos at the recent RISC-V Summit, Santa Clara.

I am really excited to announce that one of our partners has just taped out a Server class SoC with our Akeana 5000 series and Akeana 1000 series with multi-threading and using our multi-core coherent mesh interconnect fabrics. We believe this SoC will be a pioneer RVA23 compliant multi-core RISC-V Server chip. Once the silicon is available and on boards, our software partners are keen to get to porting and running code on this SoC.

We are also working on Automotive Functional Safety compliance and going through certification with our products for our Automotive customers.

How do customers normally engage with your company?

Once the customer decides to move forward, a license agreement is completed for full delivery of our Soft IP products for the customers’ SoC design completion and tape out.

Comments

There are no comments yet.

You must register or log in to view/post comments.