NVIDIA-Driven Demand Spurs TSMC’s Advanced Packaging Expansion Amid CoWoS Boom

TSMC Ramps Up Capacity with New Fabs Across Taiwan to Meet Surging CoWoS and AI Market Needs

Total CoWoS Capacity (WPM= Wafer Per Month):

Source: IEDM

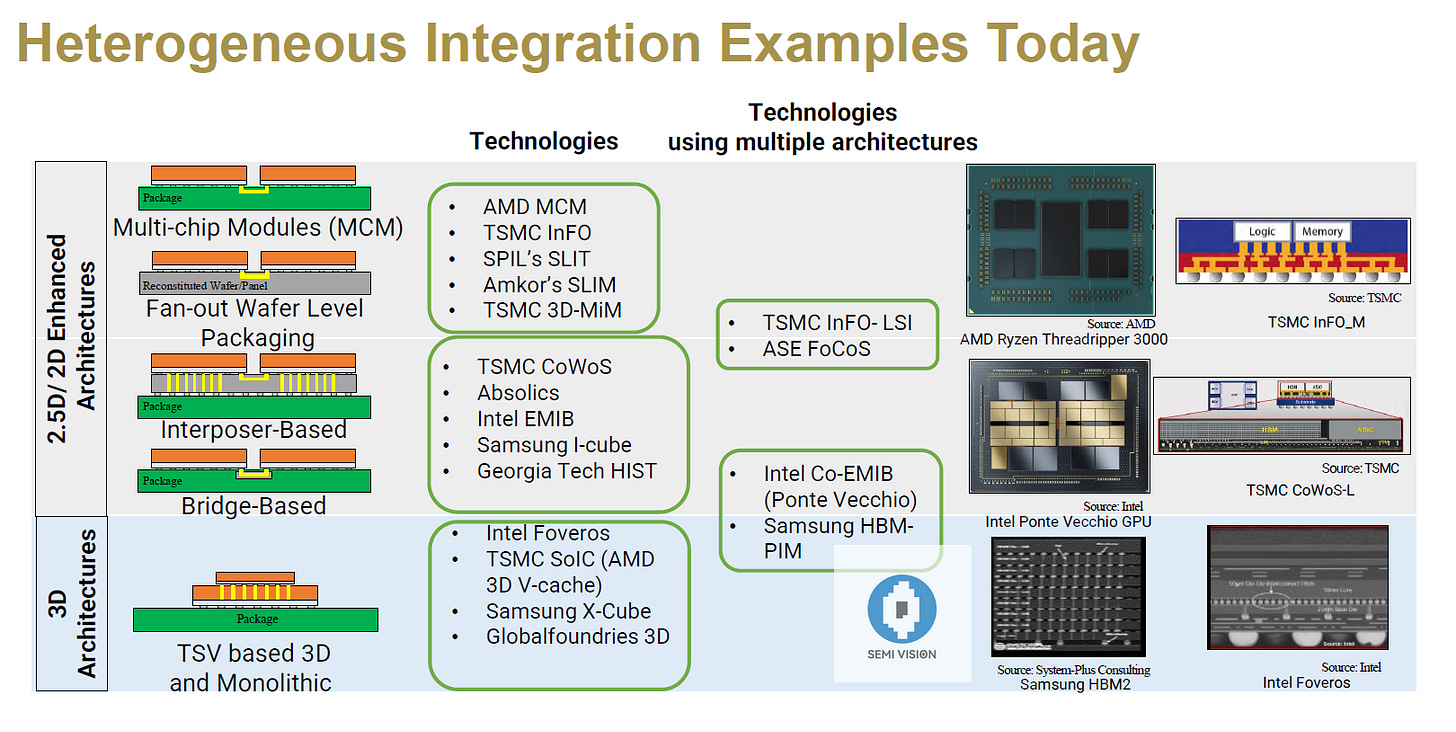

Why 3D IC packaging is better than 2.5D?

Source: SEMI Vision

Source: Nvidia

NVIDIA's high demand for CoWoS technology is primarily driven by its leadership in developing high-performance computing and artificial intelligence (AI) hardware. Key reasons for this demand include:

Source: SEMI Vision

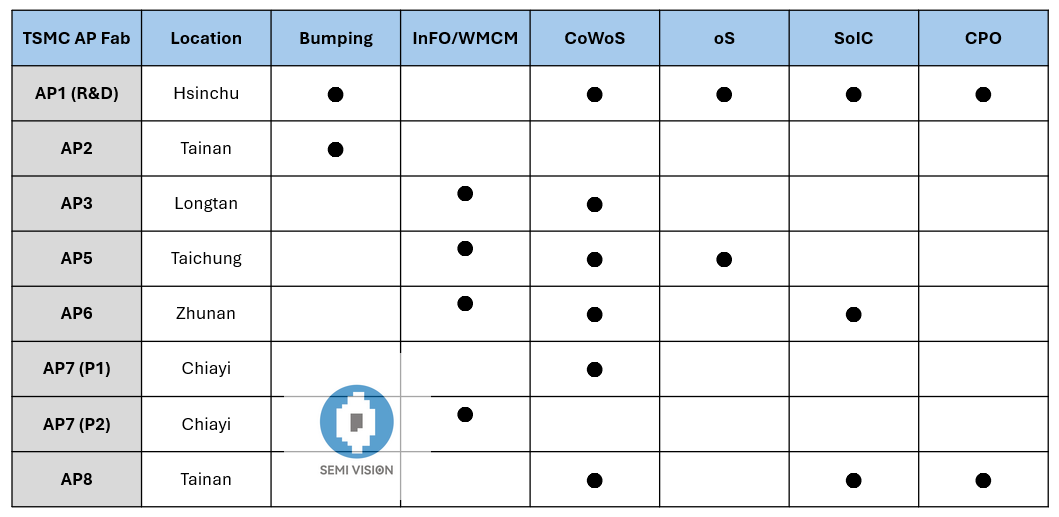

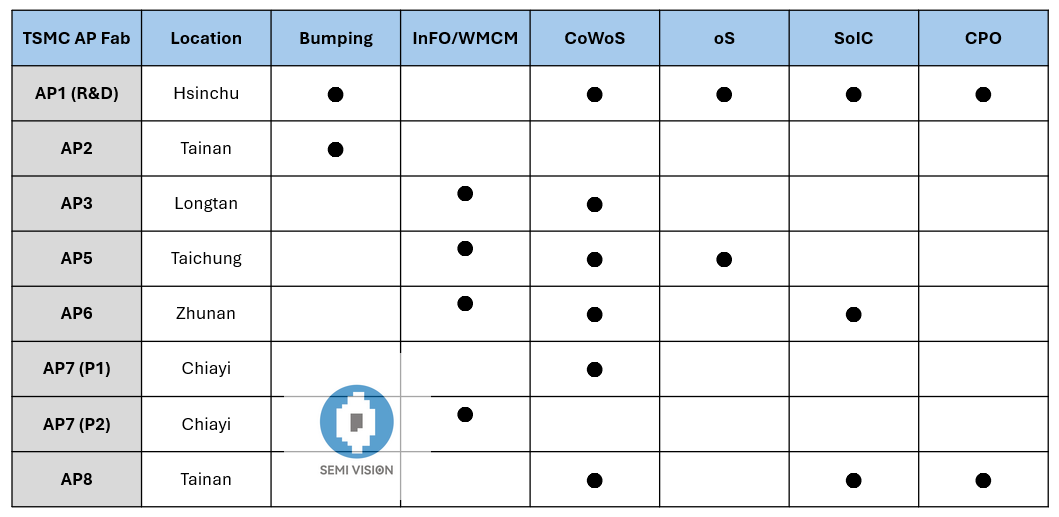

TSMC is accelerating its advanced packaging expansion efforts, with new facilities being developed in Zhunan, Chiayi, Taichung, and Tainan operating at full throttle. The advanced packaging AP6B fab in Zhunan received its usage permit on December 3, while construction on the Chiayi plant, which began in May this year, is progressing rapidly with visible steel structures taking shape. The Taichung AP5B fab is expected to commence operations in the first half of next year, and the Tainan AP8 fab (internally codenamed AP8) at Innolux's Tainan facility is slated for small-scale production by the end of 2025.

The Tainan AP8 fab is expected to gradually come online by the end of 2025. Based on estimates, the new fab will have a floor area capable of supporting a monthly capacity of 40,000 to 50,000 wafers. However, it is unlikely that TSMC will allocate the entire facility to CoWoS production. Instead, it plans to integrate capacities for SoIC (System on Integrated Chips), CP (Chip-on-Photonic Packaging), and FoPLP (Fan-Out Panel Level Packaging) as part of its strategic diversification.

Thanks for reading SEMI VISION! Subscribe for free to receive new posts and support my work. Pledge your support

TSMC Ramps Up Capacity with New Fabs Across Taiwan to Meet Surging CoWoS and AI Market Needs

Total CoWoS Capacity (WPM= Wafer Per Month):

- 2023: 13,000 ~ 16,000 WPM

- 2024: 35,000 ~ 40,000 WPM

- 2025e: 65,000 ~ 75,000 WPM

- 2026e: 90,000 ~ 110,000 WPM

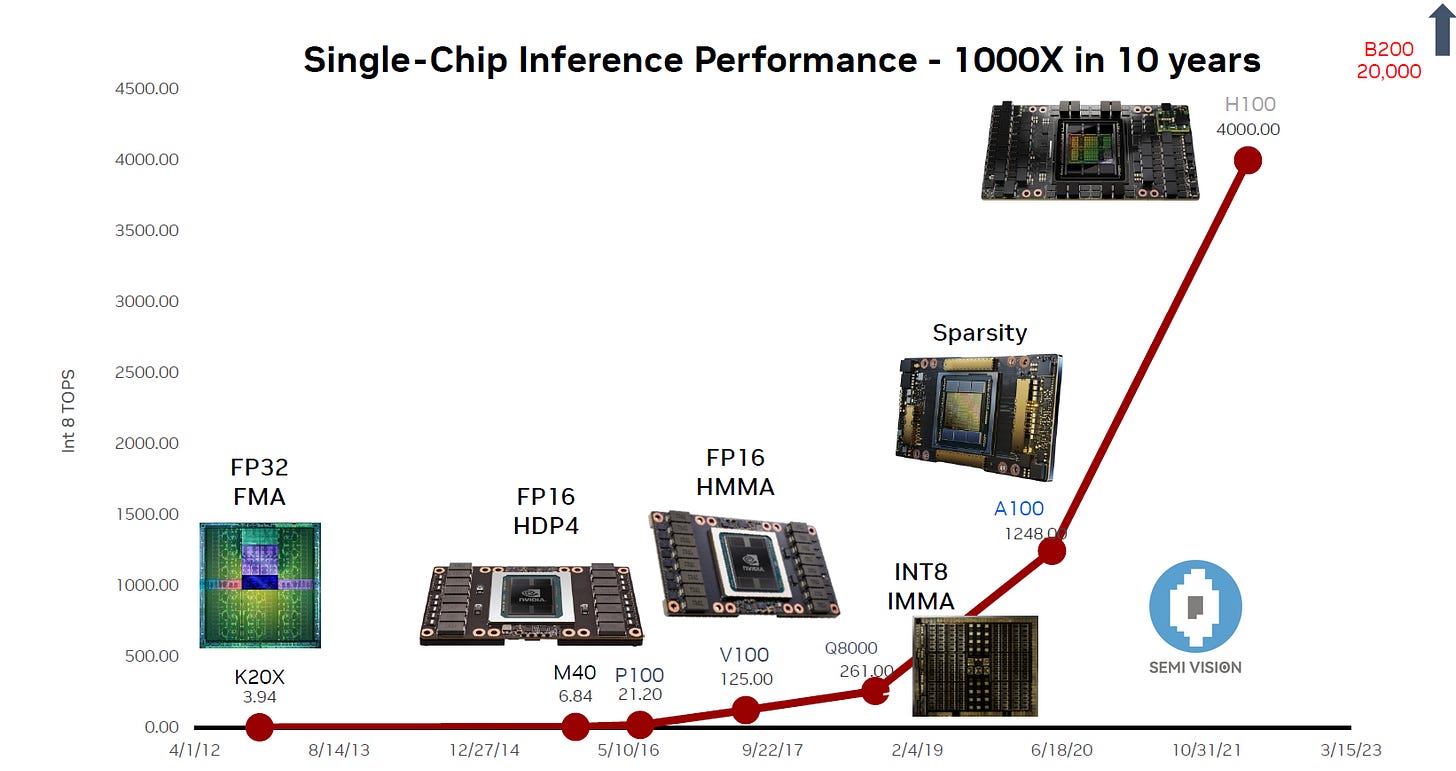

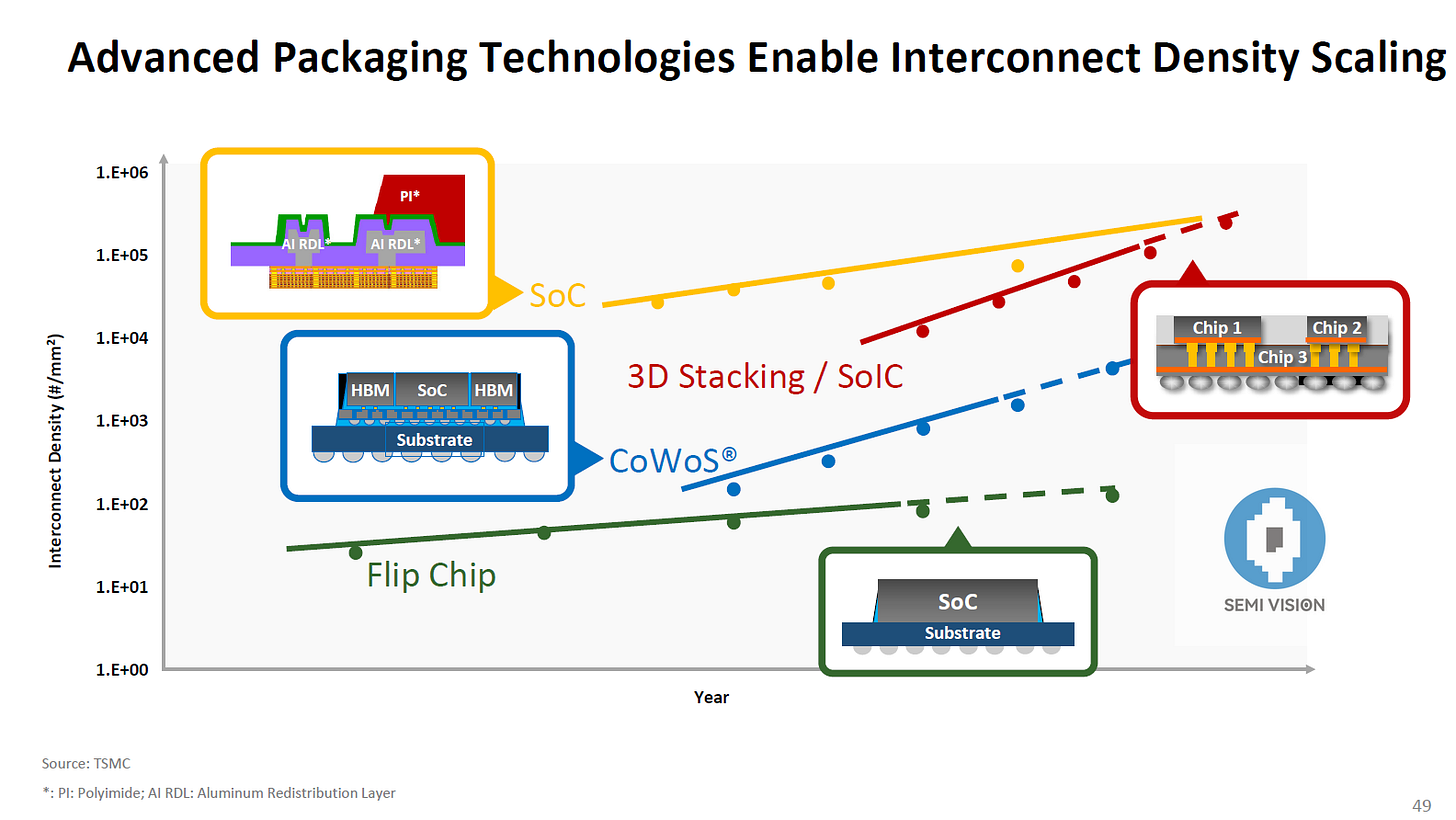

- Demand for High-Performance Computing (HPC): The increasing need for advanced AI, machine learning, and data center applications requires innovative semiconductor packaging technologies like CoWoS to handle higher computational workloads.

Source: TSMC

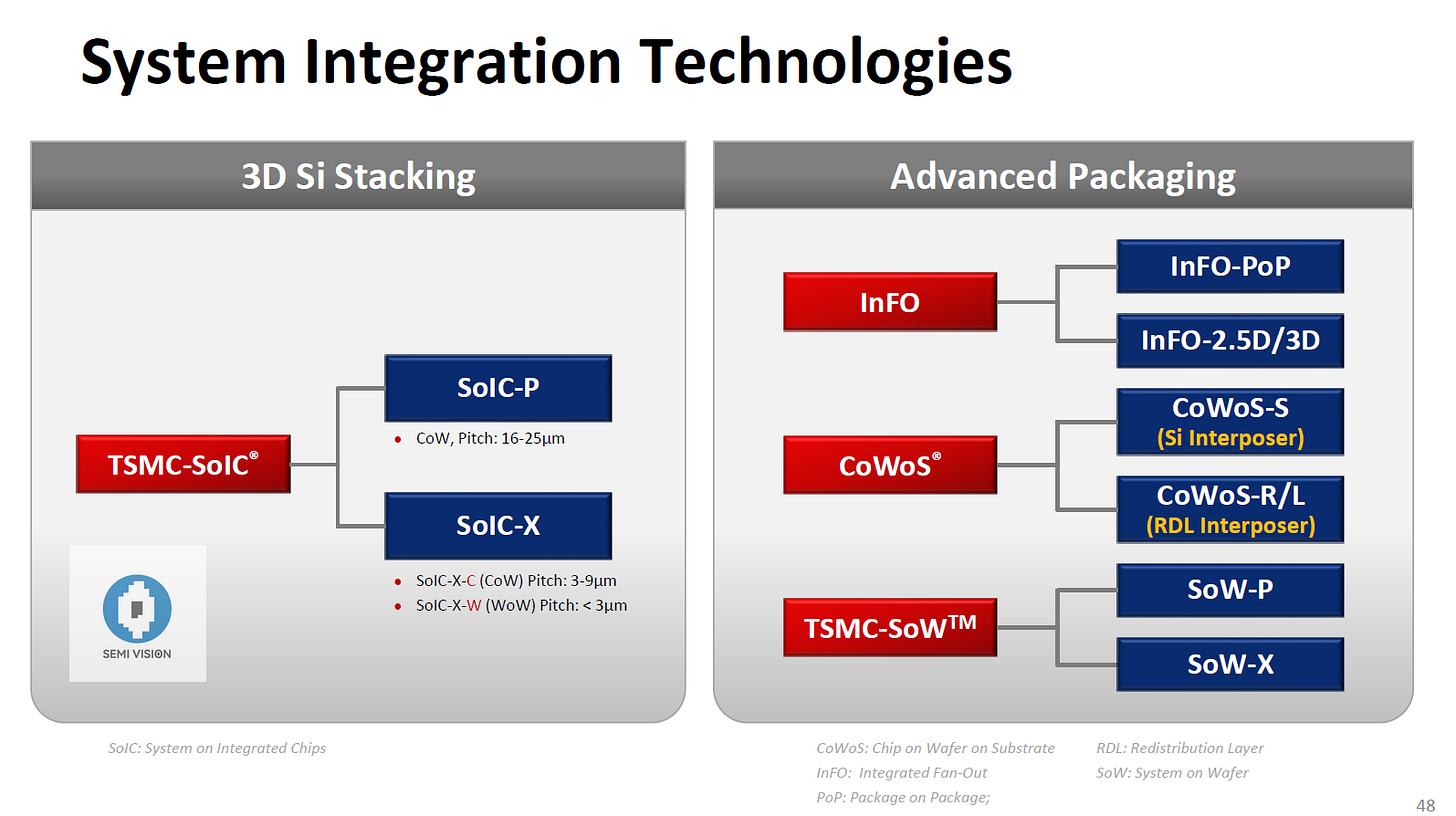

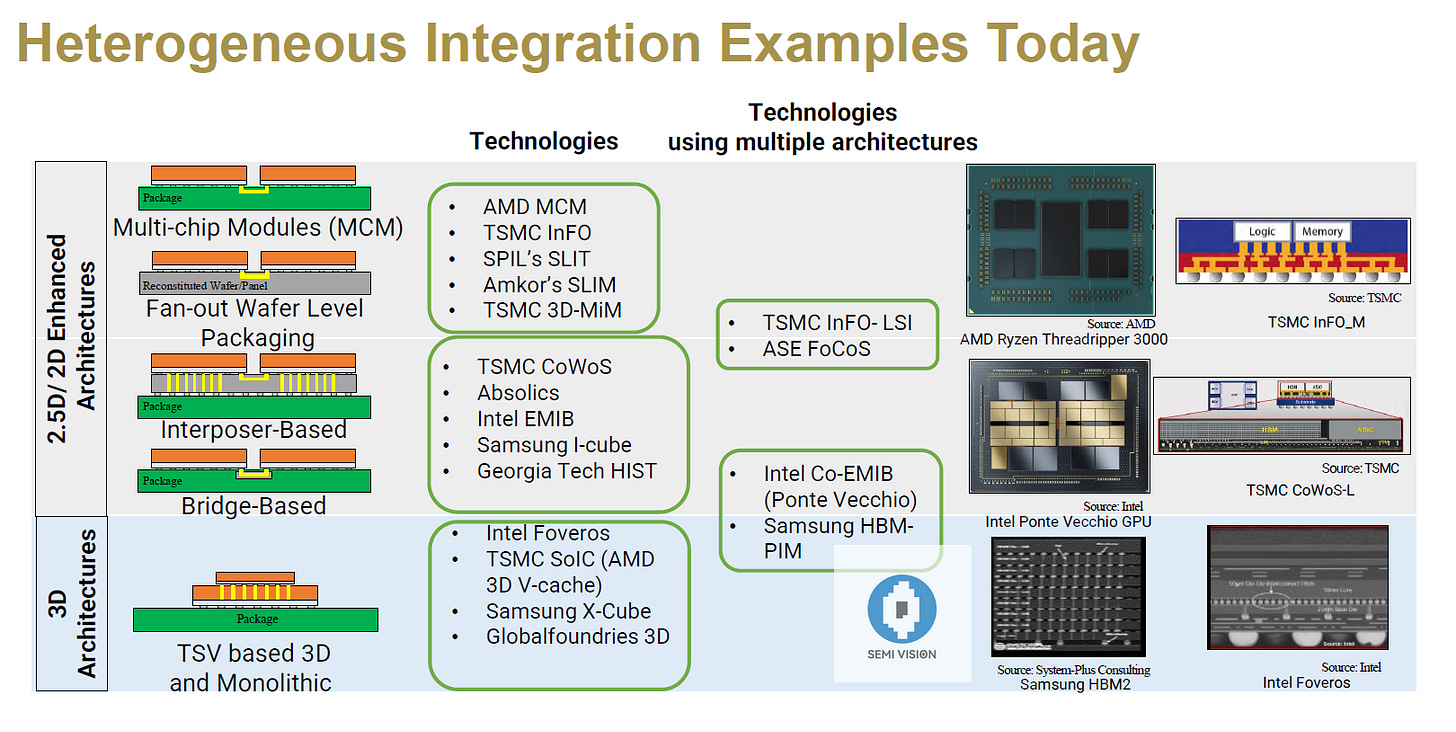

- Advancements in System Integration: CoWoS enables the integration of multiple chiplets, memory, and logic package on a single substrate, addressing the growing demand for higher bandwidth, lower latency, and improved energy efficiency.

Source: TSMC

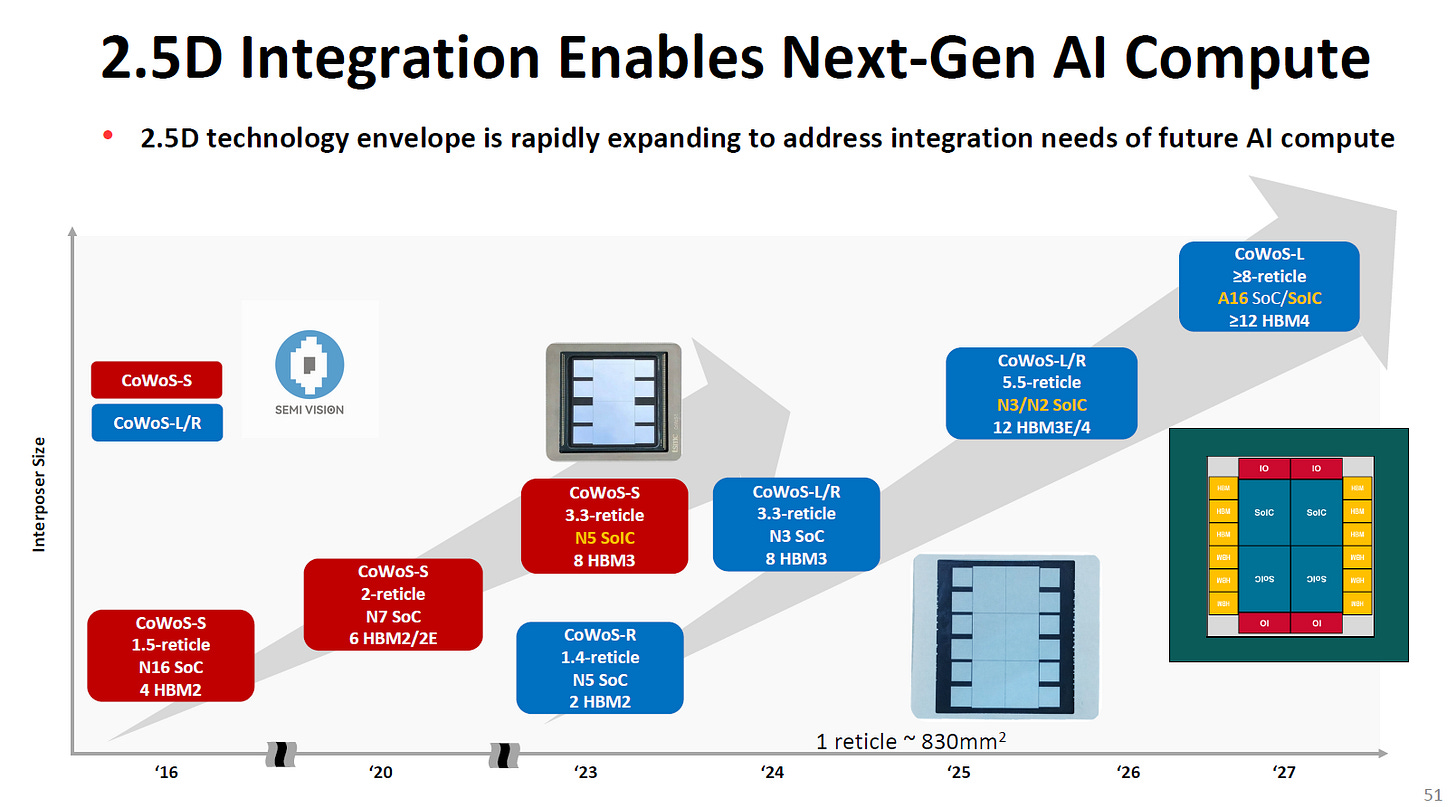

- Growing Market for 2.5D Packaging: CoWoS is a leader in 2.5D integration, which combines high-density interconnects and large-scale die integration to improve overall system performance.

Source: TSMC

- Rising Complexity of Semiconductor Designs: As semiconductor scaling becomes more challenging, CoWoS offers a scalable solution for producing heterogeneous integration chips that meet the demands of modern electronics.

Other 2D/2.5D Package Suppliers: ASE VIPack, Absolics, Intel EMIB, Samsung I-cube, Amkor, SPIL.

Source: IEDM

Why 3D IC packaging is better than 2.5D?

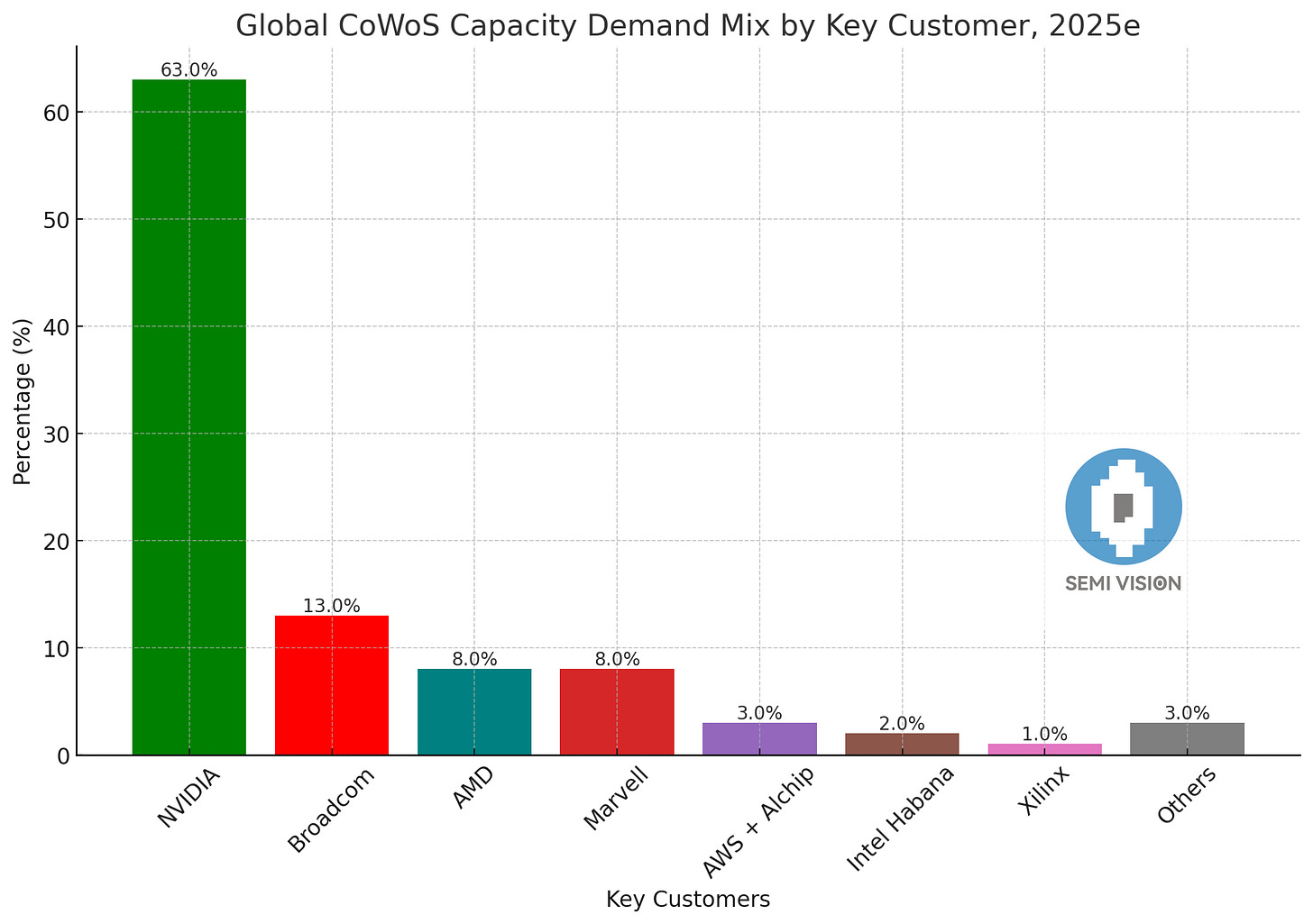

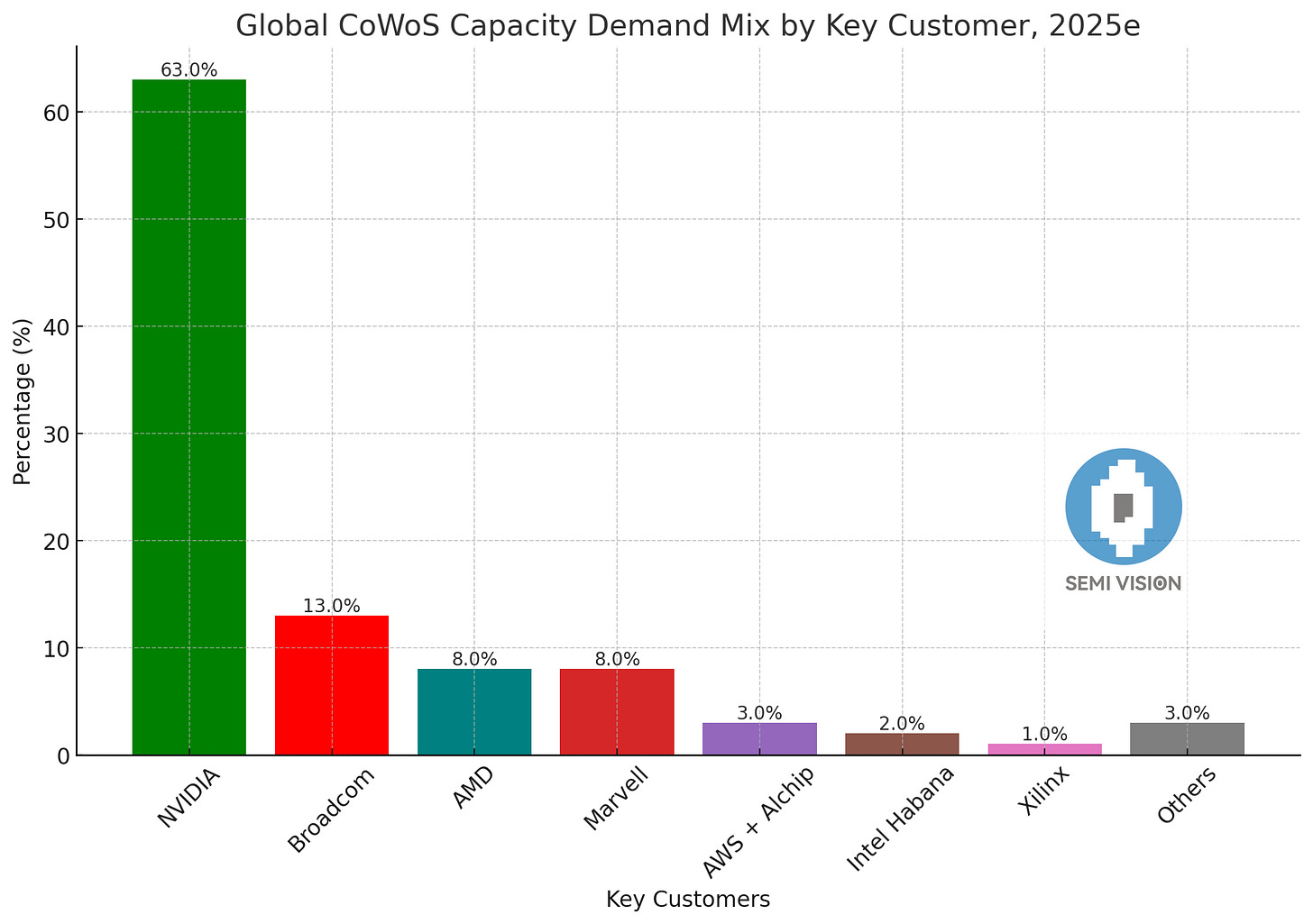

NVIDIA Leads Global CoWoS Capacity Demand Share in 2025

Source: SEMI Vision

- NVIDIA dominates the capacity demand, accounting for a significant 63% of the total demand, indicating its leadership position in adopting CoWoS technology.

- Broadcom follows at 13%, marking it as the second-largest contributor to CoWoS demand, albeit far behind NVIDIA.

- AMD and Marvell each share 8%, tying for the third spot, suggesting comparable interest in this technology from both companies.

- Other contributors, including AWS + Alchip (3%), Intel (2%), Xilinx (1%), and Others (3%), account for much smaller shares, indicating their relatively limited reliance on CoWoS capacity.

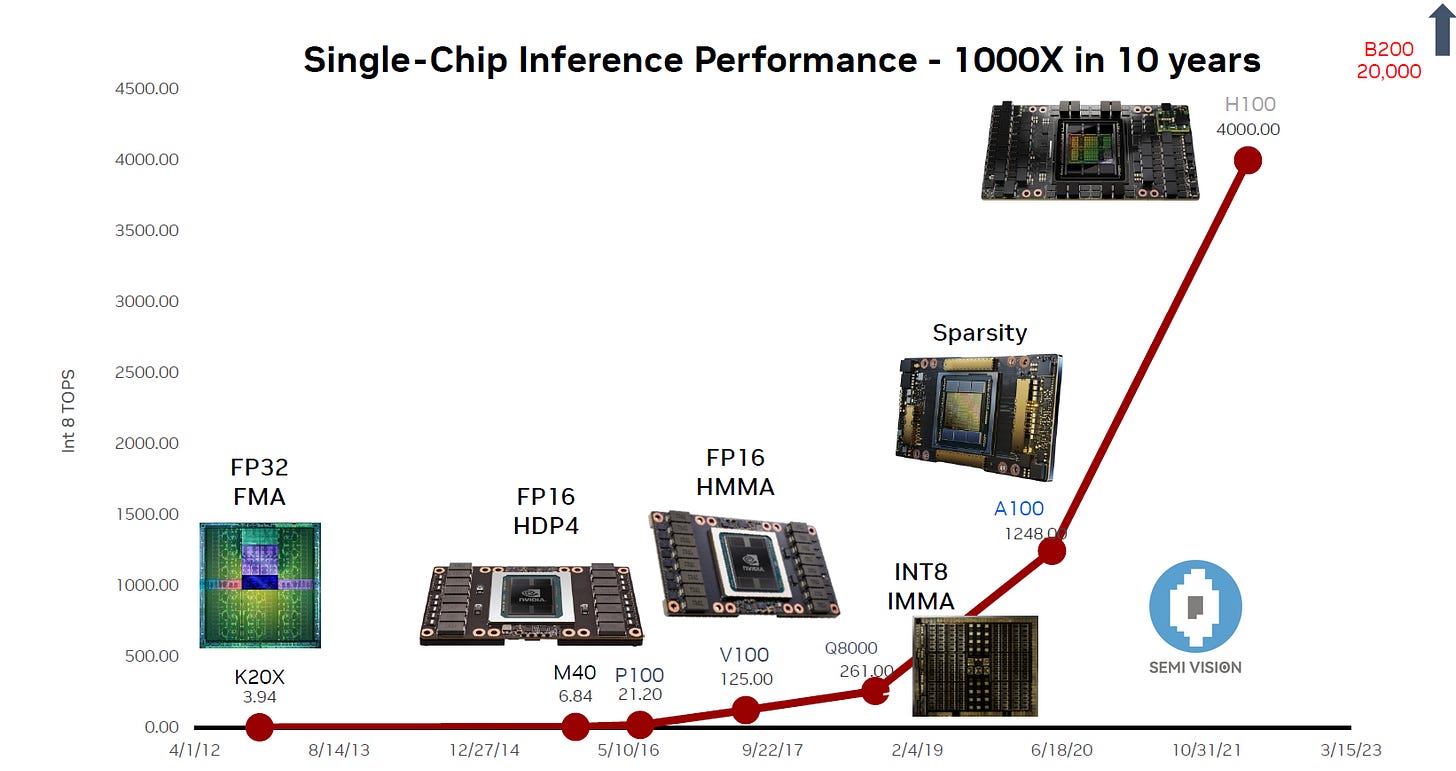

Source: Nvidia

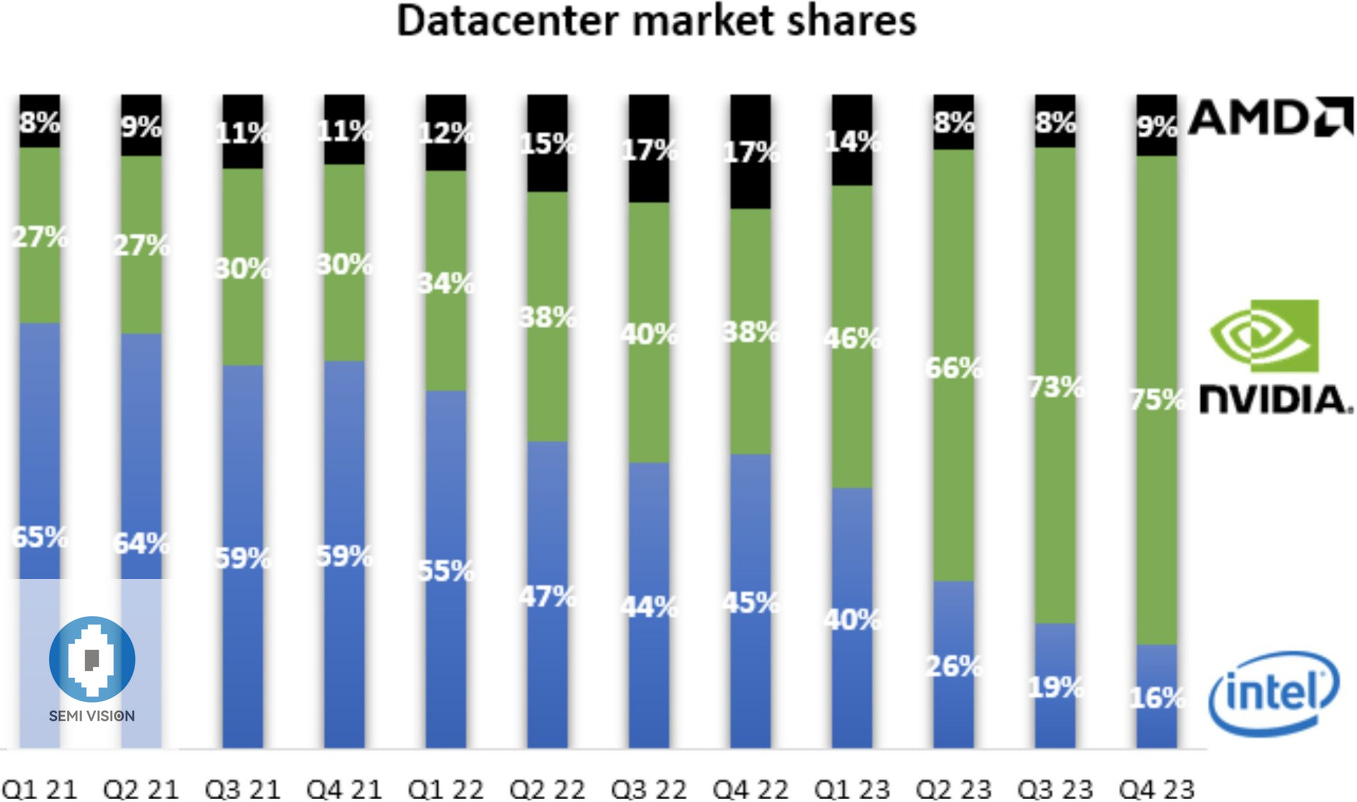

NVIDIA's high demand for CoWoS technology is primarily driven by its leadership in developing high-performance computing and artificial intelligence (AI) hardware. Key reasons for this demand include:

- Advanced Packaging for AI and HPC: CoWoS technology enables NVIDIA to package multiple high-bandwidth memory (HBM) chips with their GPUs on a single substrate. This is critical for AI training, inference and HPC, which require massive computational power and memory bandwidth.

- AI and Machine Learning Boom: NVIDIA's GPUs are at the core of AI and machine learning systems globally. The rapid growth in AI applications across industries has significantly increased the need for advanced packaging solutions like CoWoS to meet performance demands.

- Leadership in Data Centers: NVIDIA dominates the data center market, where its GPUs are used for large-scale AI training and inference tasks. CoWoS technology allows for higher performance and energy efficiency, making it essential for NVIDIA's data center products.

Source: Jesse Cohen

- Chiplet Architecture: CoWoS supports NVIDIA’s move towards chiplet-based architectures, which allow for modular designs and better scalability. This is especially important for its next-generation products.

- Demand from Key Industries: Industries such as Gen AI, LLMs, autonomous vehicles, and scientific research heavily rely on NVIDIA GPUs for AI-driven solutions, further driving the demand for CoWoS technology to deliver cutting-edge performance.

TSMC Ramps Up CoWoS Capacity Expansion: Advanced Packaging Plants in Full Swing Across Taiwan!

Source: SEMI Vision

TSMC is accelerating its advanced packaging expansion efforts, with new facilities being developed in Zhunan, Chiayi, Taichung, and Tainan operating at full throttle. The advanced packaging AP6B fab in Zhunan received its usage permit on December 3, while construction on the Chiayi plant, which began in May this year, is progressing rapidly with visible steel structures taking shape. The Taichung AP5B fab is expected to commence operations in the first half of next year, and the Tainan AP8 fab (internally codenamed AP8) at Innolux's Tainan facility is slated for small-scale production by the end of 2025.

The Tainan AP8 fab is expected to gradually come online by the end of 2025. Based on estimates, the new fab will have a floor area capable of supporting a monthly capacity of 40,000 to 50,000 wafers. However, it is unlikely that TSMC will allocate the entire facility to CoWoS production. Instead, it plans to integrate capacities for SoIC (System on Integrated Chips), CP (Chip-on-Photonic Packaging), and FoPLP (Fan-Out Panel Level Packaging) as part of its strategic diversification.

Thanks for reading SEMI VISION! Subscribe for free to receive new posts and support my work. Pledge your support