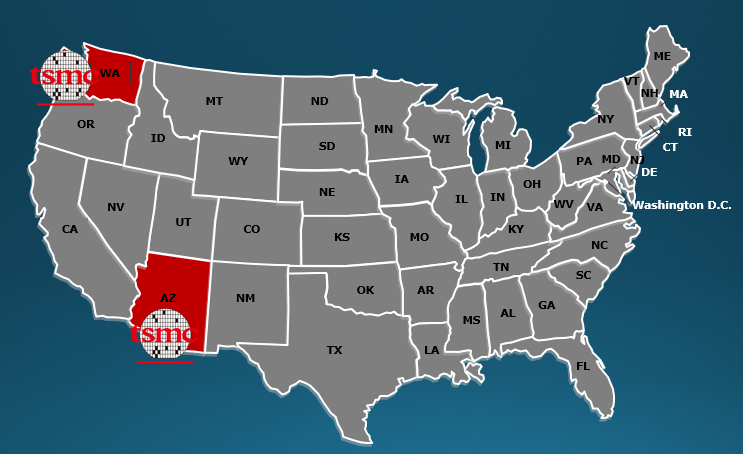

After following the discussion about wafer pricing for 3nm TSMC wafers in another thread, I did a back-of-the-envelope calculation based on the numbers TSMC released about their Arizona Investment, depreciation assumptions and an assumption on the split between facilities and equipment invest for the site.

Data Input: there will be $40B investment for 600k WOPY.

Assumption 1: there is an 80/20 split between equipment and facilities (it is likely a bit higher for equipment, I used this more conservative estimate, as facilities/building depreciation is stretched over more years than equipment, resulting in less wafer cost from that portion)

Assumption 2: the depreciation for facilities is scheduled linearly for 20 years, for equipment it is either (2a) 5 years (standard?) or (2b) 8 years (extended)

Assumption 3: there are ~80 mask layers for an average $25 cost per mask layer (not including depreciation and amortization, but including facilities, materials, labor), resulting in ~$2k of operating cost per Wafer.

The high level cost model (CM) looks as follows:

TSMC is reporting gross marging with Depreciation included in COGS, and Margin is defined as Margin = (Revenue - COGS / Revenue), so if we want to know revenue per wafer, we need to use the following formular:

Revenue = COGS/ (1-Margin)

TSMC's Q3'22 margin was 60.4%

Depending on what TSMC's Arizona Fab margin goals are, the total revenue per wafer would have to be between $18.6k under CM2 and a 50% margin on the low side, and $33k under CM1 and a 60% margin on the high side.

TSMC's major customers are likely paying less than the numbers above for their wafers as co-investment into new fab ramps would reduce their respective wafer costs. This might make comparison between TSMCs customers quite challenging, especially when we get only partial information from some of our industry contacts (e.g. just learning about what Apple pays per wafer, without accounting for potential co-investments).

Looking forward to feedback and a healthy discussion - I may have made mistakes in my formulas and assumptions, so corrections are very welcome.

Data Input: there will be $40B investment for 600k WOPY.

Assumption 1: there is an 80/20 split between equipment and facilities (it is likely a bit higher for equipment, I used this more conservative estimate, as facilities/building depreciation is stretched over more years than equipment, resulting in less wafer cost from that portion)

Assumption 2: the depreciation for facilities is scheduled linearly for 20 years, for equipment it is either (2a) 5 years (standard?) or (2b) 8 years (extended)

Assumption 3: there are ~80 mask layers for an average $25 cost per mask layer (not including depreciation and amortization, but including facilities, materials, labor), resulting in ~$2k of operating cost per Wafer.

The high level cost model (CM) looks as follows:

- CM1: Based on Assumption 1+2a+3, the depreciation + operations cost per wafer is estimated $13.3k

- CM2: Based on 1+2b+3 (using the extended depreciation of 8 years for the equipment), the total cost per wafer is $9.3k

TSMC is reporting gross marging with Depreciation included in COGS, and Margin is defined as Margin = (Revenue - COGS / Revenue), so if we want to know revenue per wafer, we need to use the following formular:

Revenue = COGS/ (1-Margin)

TSMC's Q3'22 margin was 60.4%

Depending on what TSMC's Arizona Fab margin goals are, the total revenue per wafer would have to be between $18.6k under CM2 and a 50% margin on the low side, and $33k under CM1 and a 60% margin on the high side.

TSMC's major customers are likely paying less than the numbers above for their wafers as co-investment into new fab ramps would reduce their respective wafer costs. This might make comparison between TSMCs customers quite challenging, especially when we get only partial information from some of our industry contacts (e.g. just learning about what Apple pays per wafer, without accounting for potential co-investments).

Looking forward to feedback and a healthy discussion - I may have made mistakes in my formulas and assumptions, so corrections are very welcome.