- This event has passed.

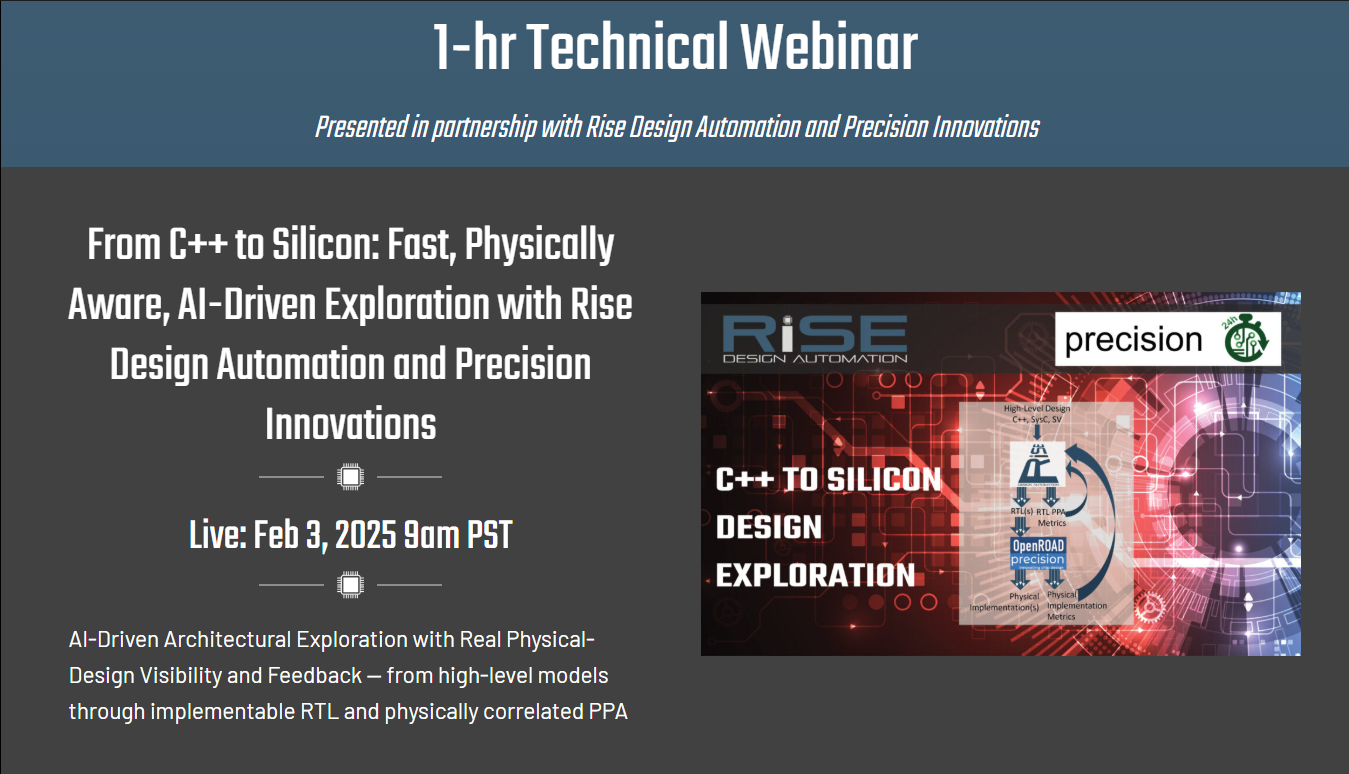

Webinar: From C++ to Silicon: Fast, Physically Aware, AI-Driven Exploration with Rise Design Automation and Precision Innovations

As hardware designs grow more complex, architectural exploration is increasingly critical to delivering differentiated silicon. Teams frequently develop promising architectures only to discover late in the cycle that physical implementation is too costly or fails to meet key specifications. This challenge intensifies as designers integrate new accelerators — video, audio, ML, or custom datapaths — rapidly expanding the search space.

AI-based automation can help, but only when each exploration trial provides cost metrics (area, timing, power) that are both fast and credible. Traditional parameter sweeps are slow. Full physical analysis is expensive. And without correlation to real implementation costs, AI-guided exploration can simply produce the wrong answers faster.

Rise Design Automation and Precision Innovations are partnering to change this dynamic. Together, they deliver fast, accurate, physically aware exploration loops — ideal for reinforcement learning, iterative refinement, and high-volume experimentation.

Rise Design Automation provides 10× faster High-Level Synthesis (HLS) with timing and area correlation within a few percent of downstream RTL-synthesis results. The Rise toolchain can also execute downstream tools “under the hood” and incorporate their feedback directly into HLS. Integrating Precision Innovations’ industry ready OpenROAD-based RTL→GDSII flow and OpenROAD Flow Scripts adds production-grade physical estimation with strong area and timing accuracy validated down to advanced nodes (including 2–3nm).

Combined, this integrated flow enables rapid exploration from high-level C++/SystemC/SystemVerilog through synthesized RTL to physically correlated PPA — supporting hundreds or thousands of trials without licensing barriers.

This session demonstrates how an integrated, AI-driven architectural exploration solution from Rise Design Automation and Precision Innovations provides rapid, actionable feedback to guide design decisions, and how you benefit from these capabilities in your own design flow.

What You’ll Learn

In this technical deep dive, you’ll see how Rise Design Automation and Precision Innovations help you:

- Run AI-guided architectural exploration with fast, physically grounded cost metrics

- Model and explore designs in C++, SystemC, or SystemVerilog and automatically generate multiple RTL variants

- Use Rise’s fast, correlated HLS engine to accelerate exploration with credible RTL-level PPA

- Leverage Precision’s OpenROAD-based RTL→GDSII flow for production-grade physical estimation — enabling early visibility into area, timing, and implementation feasibility

- Apply reinforcement learning and design agents to guide the search toward optimal architectures

- Scale exploration across hundreds or thousands of trials without restrictive per-run licensing

This webinar highlights practical techniques to accelerate exploration, increase confidence, and improve architectural decisions earlier in the design process.

Live Demonstration

See a complete exploration loop from high-level behavioral model through Rise Design Automation’s HLS, through RTL synthesis, and into Precision Innovations’ OpenROAD-based physical estimator — with AI-guided refinement driven by real PPA feedback

Who Should Attend:

Hardware architects, design engineers, verification leads, and research teams who want to:

- Accelerate architectural exploration for complex accelerators

- Apply AI/ML or reinforcement-learning workflows to silicon design

- Improve correlation between high-level design, RTL, and physical estimates

- Confidently explore many architectural options without slow iteration loops

- Shift verification and physical awareness earlier in the flow

- Deploy scalable exploration without restrictive per-run licensing

Whether you’re adding a new accelerator to an SoC or exploring ML-driven design automation, this session provides a practical foundation for leveraging Rise + Precision.

Details

- Date: February 3

-

Time:

9:00 AM - 10:00 AM

- Event Tags:openroad, precision innovations, Rise Design Automation, webinar

- Website: https://www.rise-da.com/rise-precision-registration/?utm_source=Email&utm_medium=Blast1&utm_campaign=Precision

Organizer

- Rise Design Automation

- View Organizer Website

Venue

- Virtual

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center