The world semiconductor market was $208 billion in third-quarter 2025, according to WSTS. This marks the first time the market has been above $200 billion. 3Q 2025 was up 15.8% from 2Q 2025, the highest quarter-to-quarter growth since 19.9% in 2Q 2009. 3Q 2025 was up 25.1% from 3Q 2024, the highest growth versus a year earlier since… Read More

Boosting SoC Design Productivity with IP-XACT

IP-XACT, defined by IEEE 1685, is a standard that pulls together IP packaging, integration, and reuse. For anyone building modern SoCs (Systems on Chip), IP-XACT isn’t just another XML schema: it is a productivity multiplier and a risk-reduction tool that brings order to your electronic system design.

What is IP-XACT?

IP-XACT… Read More

Silicon Catalyst on the Road to $1 Trillion Industry

There were quite a few announcements at the Silicon Catalyst event at the Computer History Museum last week. The event itself was eventful with semiconductor legends in the audience and on the stage. First let’s talk about the announcements Silicon Catalyst made then we will talk about the event itself.

In addition to expanding… Read More

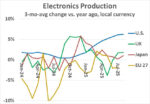

U.S. Electronics Production Growing

U.S. electronics production has been on an accelerating growth trend over the last ten months. Three-month average change versus a year ago (3/12 change) has increased from 0.4% in October 2024 to 6.2% in August 2025. Japan’s 3/12 change has been positive since November 2024, but has been decelerating for most of 2025, reaching… Read More

Webinar – The Path to Smaller, Denser, and Faster with CPX, Samtec’s Co-Packaged Copper and Optics

For markets such as data center, high-performance computing, networking and AI accelerators the battle cry is often “copper is dead”. The tremendous demands for performance and power efficiency often lead to this conclusion. As is the case with many technology topics, things are not always the way they seem. It turns out a lot … Read More

The 2025 Semi Industry Forum: On the Road to a $1 Trillion Industry

The global semiconductor industry stands at a defining moment in its history. Having surpassed $600 billion in annual revenue, the path to a $1 trillion market is no longer a distant dream but an achievable milestone within the next decade. The annual 2025 Semi Industry Forum, organized by Silicon Catalyst, brings together the… Read More

SEMICON West AZ- Congress & China- Memory Madness- AI Semiconductor Tsunami

– First SEMICON in Arizona was great- should make it permanent

– Congress finally wakes up to China issues long after cows are gone

– Memory cycle in support of AI could be huge but scary at same time

– AI demand seems bottomless- but may distort chip industry dynamics

Phoenix SEMICON was wonderful!

The crowds… Read More

Podcast EP310: On Overview of the Upcoming DVCon Europe Conference and Exhibition with Dr. Mark Burton

Daniel is joined by Dr. Mark Burton, the General Chair for this year’s DVCon Europe. DVCon is the premier conference on the application of languages, tools, and methodologies for the design and verification of electronic systems and integrated circuits.

Mark shares his long history of involvement in DVCon with Dan. He … Read More

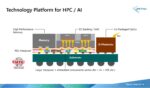

Revolutionizing AI Infrastructure: Alchip and Ayar Labs’ Co-Packaged Optics Breakthrough at TSMC OIP 2025

In the relentless race to power next-generation artificial intelligence (AI) systems, data connectivity has emerged as the critical bottleneck. As AI models balloon in size—from billions to trillions of parameters—compute resources alone are insufficient. According to Ayar Labs, approximately 70% of AI compute time is … Read More

Semiconductor Equipment Spending Healthy

Global spending on semiconductor manufacturing equipment totaled $33.07 billion in the 2nd quarter of 2025, according to SEMI and SEAJ. 2Q 2025 spending was up 23% from 2Q 2024. China had the largest spending at $11.36 billion, 34% of the total. However, China spending in 2Q 2025 was down 7% from 2Q 2024. Taiwan had the second largest… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?