IC designs have physical verification applications like Layout Versus Schematic (LVS) at the transistor-level to ensure that layout and schematics are equivalent, in addition there’s an Electrical Rules Check (ERC) for connections to well regions called a soft check. The connections to all the devices needs to have the most… Read More

Electronic Design Automation

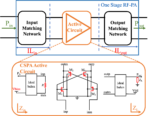

Revolutionizing RFIC Design: Introducing RFIC-GPT

In the rapidly evolving world of Radio Frequency Integrated Circuits (RFIC), the challenge has always been to design efficient, high-performance components quickly and accurately. Traditional methods, while effective, come with a high complexity and a lengthy iteration process. Today, we’re excited to unveil RFIC-GPT… Read More

2024 Signal & Power Integrity SIG Event Summary

It was a dark and stormy night here in Silicon Valley but we still had a full room of semiconductor professionals. I emceed the event. In addition to demos, customer and partner presentations, we did a Q&A which was really great. One thing I have to say is that Intel really showed up for both DesignCon and the Chiplet Summit. Quite… Read More

BDD-Based Formal for Floating Point. Innovation in Verification

A different approach to formally verifying very challenging datapath functions. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue our series on research ideas. As always, feedback welcome. We’re planning to add a wrinkle… Read More

New Emulation, Enterprise Prototyping and FPGA-based Prototyping Launched

General purpose CPUs have run most EDA tools quite well for many years now, but if you really want to accelerate something like simulation then you start to look at using specializedhardware accelerators. . Emulators came onto the scene around 1986 and the processing power has greatly increased over the years, mostly in response… Read More

Photonic Computing – Now or Science Fiction?

Cadence recently held an event to dig into the emerging world of photonic computing. Called The Rise of Photonic Computing, it was a two-day event held in San Jose on February 7th and 8th. The first day of the event was also accessible virtually. I attended a panel discussion on the topic – more to come on that. The day delivered a rich… Read More

Achieving Extreme Low Power with Synopsys Foundation IP Memory Compilers and Logic Libraries

The relentless demand for lower power SoCs is evident across many markets. Examples include cutting-edge mobile, IoT, and wearable devices along with the high compute demands for AI and 5G/6G communications. Drivers for low power include battery life, thermal management and, for high compute applications, the overall cost… Read More

Navigating the 1.6Tbps Era: Electro-Optical Interconnects and 224G Links

In the relentless pursuit of ever-increasing data speeds, the 1.6 Terabits per second (Tbps) era looms on the horizon, promising unprecedented levels of connectivity and bandwidth within data centers. As data-intensive applications proliferate and the demand for real-time processing escalates, the need for robust and efficient… Read More

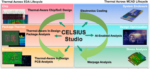

Cadence Debuts Celsius Studio for In-Design Thermal Optimization

Continuing the multiphysics theme, I talked recently with Melika Roshandell (Product Management Director at Cadence) on the continuing convergence between MCAD and ECAD. You should know first that Melika has a PhD in mechanical engineering and an extensive background in thermal engineering at Broadcom and Qualcomm, all very… Read More

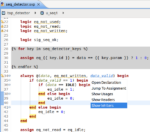

Handling Preprocessed Files in a Hardware IDE

For several years now, I’ve been meeting with AMIQ EDA co-founder Cristian Amitroaie every few months to discuss the state of the industry, key trends in design and verification, and the ways that they help facilitate and accelerate chip development. I noticed an interesting new feature mentioned in their latest press release… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry