The semiconductor industry is facing a paradigm shift. Traditional scaling, once driven by Moore’s Law, is slowing down. For years, moving to smaller process nodes led to lower transistor costs and better performance. However, scaling from node to node now offers fewer benefits as wafer costs rise much more than the historical… Read More

Tag: through silicon vias

Chiplets-Based Systems: Keysight’s Role in Design, Testing, and Data Management

Keysight, with deep roots tracing back to Hewlett-Packard, has long been at the forefront of innovation in electronic design and testing. It manufactures electronics test and measurement equipment and software. The company also owns its own foundry and makes custom chips and packages for its instrumentation business. Many… Read More

Ensuring 3D IC Semiconductor Reliability: Challenges and Solutions for Successful Integration

One of the most promising advancements in the semiconductor field is the development of 3D Integrated Circuits (3D ICs). 3D ICs enable companies to partition semiconductor designs and seamlessly integrate silicon Intellectual Property (IP) at the most suitable process nodes and processes. This strategic partitioning yields… Read More

Enabling Next Generation Silicon In Package Products

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

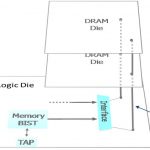

Testing an IC Sandwich

At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

Testing, testing… 3D ICs

3D ICs complicate silicon testing, but solutions exist now to many of the key challenges. – by Stephen Pateras

The next phase of semiconductor designs will see the adoption of 3D IC packages, vertical stacks of multiple bare die connected directly though the silicon. Through-silicon vias (TSV) result in shorter and thinner… Read More