In a warmly received keynote at the RISC-V Summit, computer architecture legend David Patterson took the audience on a captivating trip back to 1981, using scanned versions of his original overhead transparencies to recount the birth of Reduced Instruction Set Computing (RISC) at UC Berkeley.

Patterson began with humor, noting… Read More

In an engaging presentation at a recent RISC-V summit, Martin Dixon, Google’s Director of Data Center Performance Engineering, took the audience on a metaphorical “road trip” to explore the company’s vision for integrating RISC-V into its massive warehouse-scale computing infrastructure. Drawing… Read More

Building a complex SoC is a risky endeavor that demands careful planning, strategic decisions, and collaboration across hardware and software domains. As highlighted in Darren Jones’ RISC-V Summit presentation from Andes Technology, titled “From Blueprint to Reality: Navigating SoC Tradeoffs, IP, and Ecosystem,”… Read More

RISC-V has emerged as a cornerstone of modern computing, offering an open-source alternative to proprietary designs like ARM and x86. Free from licensing fees and highly extensible, RISC-V powers everything from IoT devices to AI accelerators, with over 13 billion cores shipped globally. Annual RISC-V Summits, organized… Read More

Daniel is joined by Andrea Gallo, CEO of RISC-V International. Before joining RISC-V he worked in leadership roles at Linaro for over a decade and before Linaro he was a fellow at STMicroelectronics.

Dan explores the current state of the RISC-V movement with Andrea, who describes the focus and history of this evolving standard.… Read More

Founded with a vision to create transformative, customizable IP solutions, Semidynamics has emerged as a significant player in the AI hardware industry. Initially operating as a design engineering company, Semidynamics spent its early years exploring various pathways before pivoting to develop proprietary intellectual… Read More

Dan is joined by Andrea Gallo, Vice President of Technology at RISC-V International. Andrea heads up the Technical Activities in collaboration with RISC-V members across workgroups and committees in growing the adoption of the RISC-V Instruction Set Architecture. Prior to RISC-V International, Andrea held multiple roles… Read More

Dan is joined by Calista Redmond, CEO of RISC-V International. Prior to RISC-V International, Calista held a variety of roles at IBM, including vice president of IBM Z Ecosystem where she led strategic relationships across software vendors, system integrators, business partners, developer communities, and broader engagement… Read More

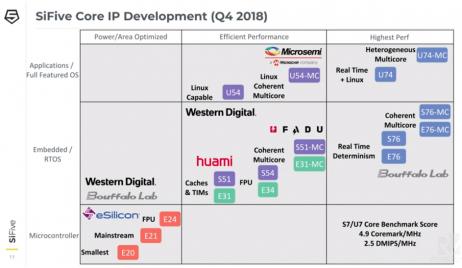

These were the closing words Yunsup Lee, CTO, SiFive used at one of the December RISC-V Summit Keynotes entitled ‘Opportunities and Challenges of Building Silicon in the Cloud’. Fired up was more the mood among the 1000+ attendees of the RISC-V Summit held at the Santa Clara Convention Center and SiFive was among the companies showcasing… Read More

One of the challenges in the RISC-V bid for world domination may be security. That may seem like a silly statement, given that security weaknesses are invariably a function of implementation and RISC-V doesn’t define implementation, only the instruction-set architecture (ISA). But bear with me. RISC-V success depends heavily… Read More