I want to compliment ChipGuy on a very nice write-up of a complex topic – how to model process variation in static timing.

… Read More

Tag: isadore katz

In Low Voltage Timing, the Center Cannot Hold

When I started discussing this topic with Isadore Katz, I was struggling to find a simple way to explain what he was telling me – that delay and variance calculations in STA tools are wrong at low voltage because the average (the center) of a timing distribution shifts from where you think it is going to be. He told me that I’m not alone… Read More

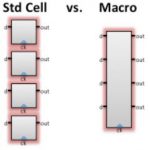

The Revenge of Microprocessor Design: The Return of the Macro

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More